# **Features**

- Highly integrated analog circuits for demodulation and decoding

- Operating voltage range: 2.3V~5.5V

- Ultra low power consumption, typical communication distance up to 10cm depending on antenna size

- Supports ISO/IEC 14443 TypeA/TypeB protocols

- Supports ISO 14443 A, B high transfer speed of 106kbit/s, 212kbit/s, 424kbit/s and 848kbit/s

- Supports MFIN/MFOUT

- · Supported host interfaces

- SPI interface up to 10Mbit/s

- I<sup>2</sup>C interface up to 400kbit/s

- Serial UART up to 1228.8kbit/s

- FIFO buffer for 64-byte transmission and reception

- · Flexible interrupt modes

- Programmable timer

- 3 power saving modes: hardware power-down, software power-down and transmitter power-down

- Internal temperature sensor automatically stops RF transmission in high chip temperature situations

- Multiple independent power supplies to avoid mutual interference between blocks and improve the operation stability

- CRC coprocessor to implement CRC and parity function

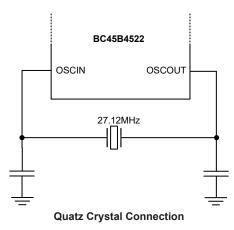

- Internal oscillator for connection to a 27.12MHz quartz crystal

- Programmable I/O pins

- Supports Low Power Card Detection (LPCD) function

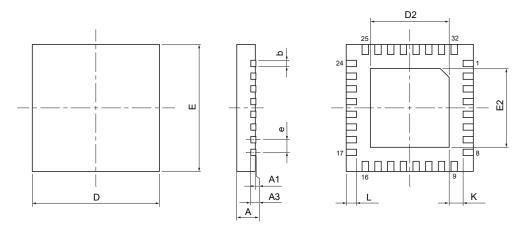

- Package type: 32-pin QFN

# Applications

- · Security access control / locks

- Toys

- · Handheld NFC readers

- · Contactless payment systems

# **General Description**

The BC45B4522 is a highly integrated reader IC for use in contactless communication at 13.56MHz. This NFC reader supports ISO/IEC 14443 A, ISO/IEC 14443B and Crypto\_M modes. The internal transmitter is able to drive the reader antenna to communicate with ISO/IEC 14443 A, ISO/IEC1444B, Crypto\_M cards and transponders without requiring additional active circuitry. The receiver block provides a robust and efficient implementation to demodulate and decode signals from ISO/IEC 14443 A, ISO/IEC1444B, Crypto\_M cards and transponders. The digital block manages the complete ISO/IEC 14443 A framing detection and error detection including parity and CRC check.

The BC45B4522 supports all protocol layers for ISO/ IEC 14443 A and ISO/IEC 14443 B communications. It supports contactless communication with higher baud rates and the bidirectional transmission speeds is up to 848kbit/s. The device provides several host interfaces including the Serial Peripheral Interface(SPI), serial UART and I<sup>2</sup>C bus.

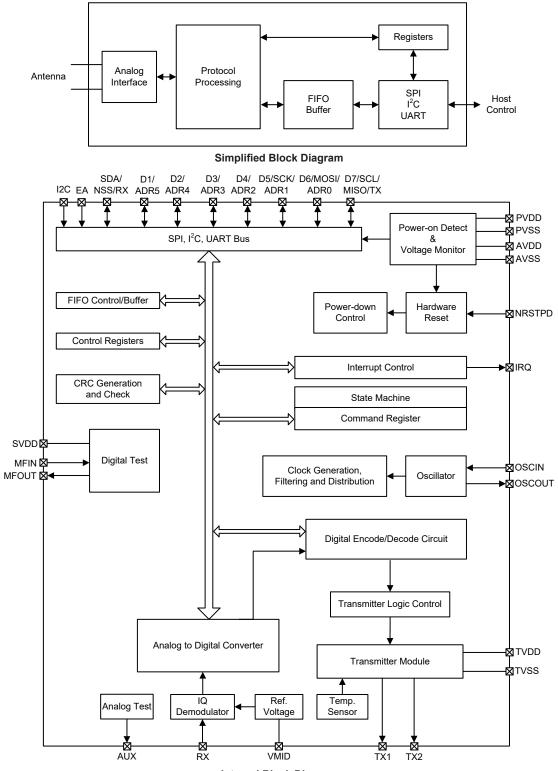

# **Block Diagram**

The analog interface is used to handle the modulation and demodulation of analog signals, and then cooperate with the host to manage the communication protocol requirements. The FIFO buffer ensures fast and convenient data transfer between the host and the contactless interface. Various host interfaces are provided to meet different customer requirements.

Internal Block Diagram

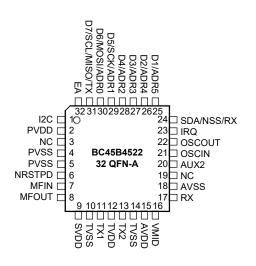

# **Pin Assignment**

# **Pin Description**

| Pin No. | Pin Name     | Pin Type | Description                                                |

|---------|--------------|----------|------------------------------------------------------------|

| 1       | I2C          | I        | I <sup>2</sup> C interface enable                          |

| 2       | PVDD         | PWR      | Pin and digital positive power supply                      |

| 3       | NC           | _        | Not connected                                              |

| 4       | PVSS         | G        | Pin and digital negative power supply, ground              |

| 5       | PVSS         | G        | Pin and digital negative power supply, ground              |

| 6       | NRSTPD       | I        | Reset or power-down pin, low active                        |

| 7       | MFIN         | I        | Test signal input                                          |

| 8       | MFOUT        | 0        | Test signal output                                         |

| 9       | SVDD         | PWR      | MFIN and MFOUT positive power supply                       |

| 10      | TVSS         | G        | Transmitter negative power supply, ground                  |

| 11      | TX1          | 0        | Transmitter antenna pin 1                                  |

| 12      | TVDD         | PWR      | Transmitter positive power supply                          |

| 13      | TX2          | 0        | Transmitter antenna pin 2                                  |

| 14      | TVSS         | G        | Transmitter negative power supply, ground                  |

| 15      | AVDD         | PWR      | Analog positive power supply                               |

| 16      | VMID         | PWR      | Internal reference voltage                                 |

| 17      | RX           | I        | Receiver antenna pin                                       |

| 18      | AVSS         | G        | Analog negative power supply, ground                       |

| 19      | NC           | _        | Not connected                                              |

| 20      | AUX2         | 0        | Test pin                                                   |

| 21      | OSCIN        | I        | 27.12MHz crystal input                                     |

| 22      | OSCOUT       | 0        | 27.12MHz crystal output                                    |

| 23      | IRQ          | 0        | Interrupt request output                                   |

| 24      | SDA/NSS/RX   | I/O      | I <sup>2</sup> C SDA; SPI NSS; UART RX                     |

| 25      | D1/ADR5      | I/O      | Programmable I/O; I <sup>2</sup> C address bit 5           |

| 26      | D2/ADR4      | I/O      | Programmable I/O; I <sup>2</sup> C address bit 4           |

| 27      | D3/ADR3      | I/O      | Programmable I/O; I <sup>2</sup> C address bit 3           |

| 28      | D4/ADR2      | I/O      | Programmable I/O; I <sup>2</sup> C address bit 2           |

| 29      | D5/SCK/ADR1  | I/O      | Programmable I/O; SPI SCK; I <sup>2</sup> C address bit 1  |

| 30      | D6/MOSI/ADR0 | I/O      | Programmable I/O; SPI MOSI; I <sup>2</sup> C address bit 0 |

| ĺ | Pin No. | Pin Name       | Pin Type                                                  | Description                             |

|---|---------|----------------|-----------------------------------------------------------|-----------------------------------------|

|   | 31      | D7/SCL/MISO/TX | Programmable I/O; I <sup>2</sup> C SCL; SPI MISO; UART TX |                                         |

|   | 32      | EA             | I                                                         | I <sup>2</sup> C address coding control |

Legend: 1. Pin Type: I=Input, O=Output, I/O=Input/Output, PWR=Power, G=Ground

2. MFIN and MFOUT are digital test pins. Leave the pins floating in product design.

# **Electrical Characteristices**

### Absolute Maximum Rating

| Symbol           | Parameter           | Conditions | Min. | Max. | Unit |

|------------------|---------------------|------------|------|------|------|

| AVDD             | Analog Power Supply | _          | -0.5 | +6.0 | V    |

| PV <sub>DD</sub> | PVDD Power Supply   | —          | -0.5 | +6.0 | V    |

| TVDD             | TVDD Power Supply   | _          | -0.5 | +6.0 | V    |

| SVDD             | SVDD Power Supply   | _          | -0.5 | +6.0 | V    |

### **Operating Condition**

| Symbol           | Parameter                       | Conditions                                                             | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------|------------------------------------------------------------------------|------|------|------|------|

| AVDD             | Analog Power Supply             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                 | 5.5  | V    |      |      |

| TV <sub>DD</sub> | Transmitter Power Supply        | PVss=AVss=TVss=0V,                                                     | 2.3  | 3.3  | 5.5  | V    |

| SVDD             | MFIN and MFOUT Pin Power Supply | PV <sub>DD</sub> ≤SV <sub>DD</sub> ≤AV <sub>DD</sub> ≤TV <sub>DD</sub> | 2.3  | 3.3  | 5.5  | V    |

| PVDD             | Pin and Digital Power Supply    |                                                                        | 2.0  | 3.3  | 5.5  | V    |

| Та               | Operating Temperature           | —                                                                      | -40  | —    | +105 | °C   |

Note: Recommended power supply condition:  $PV_{DD} \leq SV_{DD} \leq AV_{DD} \leq TV_{DD}$ . The performance of other power supply conditions are not guaranteed.

### **Power Consumption Characteristics**

| Symbol              | Parameter                           | Conditions                                                                                                                                                                | Min. | Тур. | Max. | Unit |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| 3.3V Cha            | aracteristics                       |                                                                                                                                                                           |      |      |      |      |

| I <sub>HPD</sub>    | Hardware Power-down Current         | AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =3.3V,<br>NRSTPD=LOW                                                                               | _    | 0.02 | 1.00 | μA   |

| I <sub>SPD</sub>    | Software Power-down Current         | AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =3.3V,<br>RF level detector on                                                                     | _    | 0.6  | 5.0  | μA   |

| IIDLE               | Idle Current                        | AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =3.3V                                                                                              | _    | 3.52 | 5.00 | mA   |

| I <sub>RX</sub>     | Receving Current                    | AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =3.3V                                                                                              | _    | 6.5  | 10.0 | mA   |

| I <sub>PVDD</sub>   | Pin and Digital Supply Current      | PV <sub>DD</sub> =3.3V                                                                                                                                                    | _    | 2.97 | 4.00 | mA   |

|                     | Angler Sumply Compart               | AV <sub>DD</sub> =3.3V, RcvOff=0                                                                                                                                          |      | 2.98 | 6.00 | mA   |

| AVDD                | Analog Supply Current               | AV <sub>DD</sub> =3.3V, RcvOff=1                                                                                                                                          | _    | 2.95 | 6.00 | mA   |

| I <sub>tvdd</sub>   | Transmitter Supply Current          | Continuous transmit carrier, $TV_{DD}$ =3.3V                                                                                                                              | _    | 60   | 160  | mA   |

| ILPCD               | Low Power Card Detection Current    | AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =3.3V,<br>Average current consumption in<br>LPCD mode @ WUPeriod=500ms<br>& detect wave time=5.9µs | _    | 1.5  | 10.0 | μΑ   |

| V <sub>Ripple</sub> | Power Supply Ripple Rejection       |                                                                                                                                                                           |      | _    | 400  | mV   |

| V <sub>Noise</sub>  | Power Supply Random Noise Rejection |                                                                                                                                                                           |      | _    | 1600 | mV   |

| Tosu                | Oscillator Start Up Time            |                                                                                                                                                                           |      | 300  | —    | μs   |

| Symbol              | Parameter                                                                               | Conditions                                                                                          | Min. | Тур. | Max.  | Unit |

|---------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|------|-------|------|

| 5V Char             | acteristics                                                                             |                                                                                                     |      |      |       |      |

| I <sub>HPD</sub>    | Hardware Power-down Current                                                             | $AV_{DD}=TV_{DD}=PV_{DD}=SV_{DD}=5V,$<br>NRSTPD=LOW                                                 | _    | 0.02 | 1.00  | μA   |

| ISPD                | Software Power-down Current                                                             | AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =5V,<br>RF level detector on | _    | 0.8  | 5.0   | μA   |

| IIDLE               | Idle Current AV <sub>DD</sub> =TV <sub>DD</sub> =PV <sub>DD</sub> =SV <sub>DD</sub> =5V |                                                                                                     | -    | 3.52 | 5.00  | mA   |

| I <sub>RX</sub>     | Receving Current                                                                        | AVDD=TVDD=PVDD=SVDD=5V                                                                              | _    | 6.55 | 10.00 | mA   |

| IPVDD               | Pin and Digital Supply Current                                                          | PV <sub>DD</sub> =5V                                                                                | _    | 3.2  | 5.0   | mA   |

|                     | Angler Sugaly Current                                                                   | AV <sub>DD</sub> =5V, RcvOff=0                                                                      | _    | 3.1  | 6.0   | mA   |

| AVDD                | Analog Supply Current                                                                   | AV <sub>DD</sub> =5V, RcvOff=1                                                                      | _    | 3.07 | 6.00  | mA   |

| I <sub>TVDD</sub>   | Transmitter Supply Current                                                              | Continuous transmit carrier, $TV_{DD}$ =5V                                                          | _    | 90   | 230   | mA   |

| V <sub>Ripple</sub> | Power Supply Ripple Rejection                                                           |                                                                                                     | _    | _    | 300   | mV   |

| V <sub>Noise</sub>  | Power Supply Random Noise Rejection                                                     |                                                                                                     | _    | _    | 1600  | mV   |

| Tosu                | Oscillator Start Up Time                                                                |                                                                                                     | _    | 300  | _     | μs   |

### I/O Characteristics

| Symbol            | Parameter                    | Conditions                                       | Min.                  | Тур.    | Max.                  | Unit   |

|-------------------|------------------------------|--------------------------------------------------|-----------------------|---------|-----------------------|--------|

| Pins I2C          | , EA, NRSTPD, MFIN, SDA/NSS/ | RX                                               |                       |         |                       |        |

| I <sub>LEAK</sub> | Input Leakage Current        | _                                                | -1                    | _       | 1                     | μA     |

| VIH               | High Level Input Voltage     | _                                                | $0.7 PV_{DD}$         | _       | —                     | V      |

| VIL               | Low Level Input Voltage      | _                                                | —                     | —       | 0.3PV <sub>DD</sub>   | V      |

| Pins D1/          | ADR5, D2/ADR4, D3/ADR3, D4/A | DR2, D5/SCK/ADR1, D6/MOSI/ADF                    | R0, D7/SCI            | L/MISO/ | TX, MFOU              | T, IRQ |

|                   |                              | Connected to VDD when in<br>operation/idle state | -1                    | _       | 1                     | μA     |

|                   | Input Leakage Current        | Connected to GND when in operation/idle state    | _                     | 13.5    | _                     | μΑ     |

| I <sub>LEAK</sub> |                              | Connected to 1.5V when in operation/idle state   | _                     | 13      | —                     | μA     |

|                   |                              | Left floating when in operation/idle state       | _                     | 0       | _                     | μA     |

| VIH               | High Level Input Voltage     |                                                  | 0.7PV <sub>DD</sub>   | _       | _                     | V      |

| VIL               | Low Level Input Voltage      |                                                  | _                     | _       | 0.3PV <sub>DD</sub>   | V      |

| V <sub>он</sub>   | High Level Output Voltage    |                                                  | PV <sub>DD</sub> -0.4 | _       | PVDD                  | V      |

| V <sub>OL</sub>   | Low Level Output Voltage     | _                                                | PVss                  | _       | PV <sub>ss</sub> +0.4 | V      |

| Іон               | High Level Output Current    | PV <sub>DD</sub> =3V                             | —                     | _       | 5                     | mA     |

| I <sub>OL</sub>   | Low Level Output Current     | PV <sub>DD</sub> =3V                             | —                     | —       | 14                    | mA     |

| Pins OS           | CIN, OSCOUT Connection Requ  | irements                                         |                       |         |                       |        |

| £                 | Crystal Frequency            | _                                                |                       | 27.12   | _                     | MHz    |

| f <sub>xtal</sub> | Frequency Tolerance          | _                                                | —                     | ±10     | ±20                   | ppm    |

| ESR               | Equivalent Series Resistance | _                                                |                       | _       | 100                   | Ω      |

| CL                | Load Capacitance             | _                                                | —                     | 10      | —                     | pF     |

| P <sub>xtal</sub> | Crystal Power Dissipation    | _                                                | _                     | 50      | 100                   | mW     |

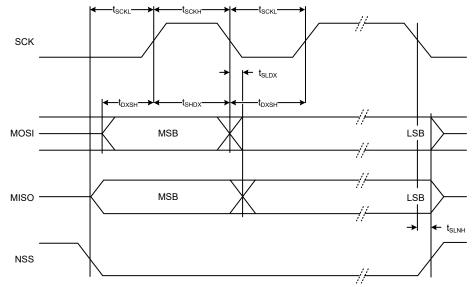

#### **SPI Characteristics**

| Symbol            | Parameter                                         | Conditions           | Min. | Тур. | Max. | Unit |

|-------------------|---------------------------------------------------|----------------------|------|------|------|------|

| t <sub>SCKL</sub> | Low Pulse Width                                   | Line SCK             | 50   | _    | _    | ns   |

| t <sub>scкн</sub> | High Pulse Width                                  | Line SCK             | 50   | _    | _    | ns   |

| t <sub>SHDX</sub> | Time Interval from SCK High to<br>Data Input Hold | SCK to changing MOSI | 25   | _    |      | ns   |

| t <sub>DXSH</sub> | Time Interval from Data Input to SCK High Set-up  | Changing MOSI to SCK | 25   | _    |      | ns   |

| t <sub>SLDX</sub> | Time Interval from SCK Low to<br>Data Output Hold | SCK to changing MISO | _    | _    | 25   | ns   |

| t <sub>SLNH</sub> | Time Interval from SCK Low to NSS High            | _                    | 25   | _    |      | ns   |

| t <sub>NHNL</sub> | NSS High Time                                     | Before communication | 50   | _    |      | ns   |

| t <sub>DOD</sub>  | Data Out Delay                                    | _                    | _    | 20   | _    | ns   |

| t <sub>DOHZ</sub> | Time Interval from Data Out to<br>High Impedance  | _                    | _    | 20   |      | ns   |

#### SPI Timing Diagram

Note: 1. The NSS signal must be low to be able to send several bytes in one data stream.2. To send more than one data stream, the NSS line must be set high between data streams.

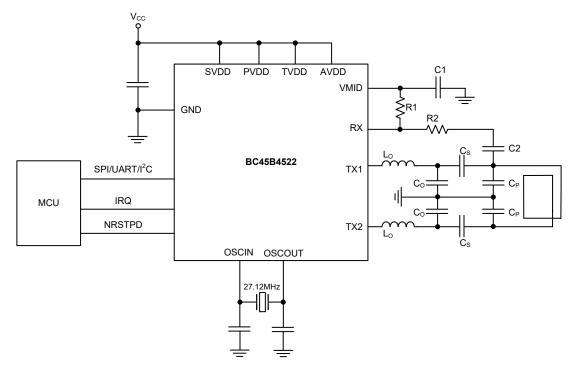

# **Typical Application Circuit**

# **Communication Interfaces**

### Overview

The BC45B4523 supports the SPI, I<sup>2</sup>C and serial UART interfaces. After reset , the device identifies the current host interface type automatically by checking the logic level on the pins. The following table lists the different connection configurations.

| Pin |      | Interfae Type |                      |

|-----|------|---------------|----------------------|

| Pin | UART | SPI           | l <sup>2</sup> C-bus |

| SDA | RX   | NSS           | SDA                  |

| I2C | 0    | 0             | 1                    |

| EA  | 0    | 1             | EA                   |

| D7  | TX   | MISO          | SCL                  |

| D6  |      | MOSI          | ADR0                 |

| D5  | —    | SCK           | ADR1                 |

| D4  |      |               | ADR2                 |

| D3  |      | _             | ADR3                 |

| D2  |      |               | ADR4                 |

| D1  | —    | —             | ADR5                 |

### **SPI Interface**

The contactless chip acts as a slave during SPI communication and uses an SPI clock signal (SCK) generated by the host. The interface can manage data speeds up to 10Mbit/s and is inaccordance with the SPI standard.

Reading data from the device using the SPI interface requires to use the byte order shown in the following table. It is possible to read out up to n data bytes.

| Pin  | Byte 0    | Byte 1    | Byte 2    | <br>Byte n    | Byte n+1 |

|------|-----------|-----------|-----------|---------------|----------|

| MOSI | Address 0 | Address 1 | Address 2 | <br>Address n | 00       |

| MISO | Х         | Data 0    | Data 1    | <br>Data n-1  | Data n   |

#### MISO and MOSI Byte Order – Read Data

Note: 1. The first sent byte defines both mode and address.

- 2. X: don't care.

- 3. The MSB must be sent first.

Writing data to the device using the SPI interface requires to use the byte order shown in the following table. It is possible to write up to n data bytes.

| Pin  | Byte 0    | Byte 1 | Byte 2 | <br>Byte n   | Byte n+1 |

|------|-----------|--------|--------|--------------|----------|

| MOSI | Address 0 | Data 0 | Data 1 | <br>Data n-1 | Data n   |

| MISO | Х         | Х      | Х      | <br>Х        | Х        |

#### MISO and MOSI Byte Order – Write Data

Note: 1. The first sent byte defines both mode and address.

- 2. X: don't care.

- 3. The MSB must be sent first.

The address byte must meet the following format, as shown in the table below.

- The MSB of the first byte defines the mode. To read data from the device, the MSB must be set to logic 1. To write data to the device, the MSB must be set to logic 0.

- Bit[6:1] defines the address.

- The LSB must be set to logic 0.

| Address<br>(MOSI) | Bit7<br>(MSB) | Bit 6   | Bit 5   | Bit4    | Bit 3   | Bit 2   | Bit 1   | Bit 0<br>(LSB) |

|-------------------|---------------|---------|---------|---------|---------|---------|---------|----------------|

| Byte 0            | 1 or 0        | Address | Address | Address | Address | Address | Address | 0              |

Address Byte

### **UART Interface**

The UART default transfer speed is 9.6kbit/s. To modify the transfer speed, the host controller must write a new value to the SerialSpeed register, where the BR\_T0[2:0] and BR\_T1[4:0] bits define the factors for setting the transfer speed. The host controller needs to first configure the register using a data rate of 9.6kbit/s, and then adjusts its data rate corresponding to the new register value.

The BR\_T0[2:0] and BR\_T1[4:0] settings are described below.

| BR_Tn        | Bit 0   | Bit 1    | Bit 2    | Bit 3    | Bit4     | Bit 5    | Bit6     | Bit 7    |

|--------------|---------|----------|----------|----------|----------|----------|----------|----------|

| BR_T0 factor | 1       | 1        | 2        | 4        | 8        | 16       | 32       | 64       |

| BR_T1 range  | 1 to 32 | 33 to 64 |

#### BR\_T0 and BR\_T1 Settings

Examples of different transfer speeds and the relevant register settings are given in the following table.

| Transfer Speed<br>(kbit/s)    | 7.2   | 9.6  | 14.4  | 19.2 | 38.4 | 57.6  | 115.2 | 128   | 230.4 | 460.8 | 921.6 | 1228.8 |

|-------------------------------|-------|------|-------|------|------|-------|-------|-------|-------|-------|-------|--------|

| SerialSpeed<br>register value | FAh   | EBh  | DAh   | CBh  | ABh  | 9Ah   | 7Ah   | 74h   | 5Ah   | 3Ah   | 1Ch   | 15h    |

| Transfer speed<br>accuracy    | -0.25 | 0.32 | -0.25 | 0.32 | 0.32 | -0.25 | -0.25 | -0.06 | -0.25 | -0.25 | 1.45  | 0.32   |

#### Selectable UART Transfer Speeds

Note: Transfer speeds exceeding 1228.8kbit/s are not supported.

The transfer speeds shown in the above table are calculated according to the following equations.

• If BR\_T0[2:0]=0

```

Transfer Speed = (27.12 \times 10^6) \div (BR \ T0+1)

```

• If BR\_T0[2:0]>0

```

Transfer Speed = (27.12 \times 10^6) \div [(BR T1+33) \div 2^{(BR_T0-1)}]

```

The UART frame format is given in this table. The LSB of the data and address bytes must be sent first. No parity bit is used during transmission.

| Bit   | Length | Value |  |  |

|-------|--------|-------|--|--|

| Start | 1-bit  | 0     |  |  |

| Data  | 8-bit  | data  |  |  |

| Stop  | 1-bit  | 1     |  |  |

#### **UART Frame Format**

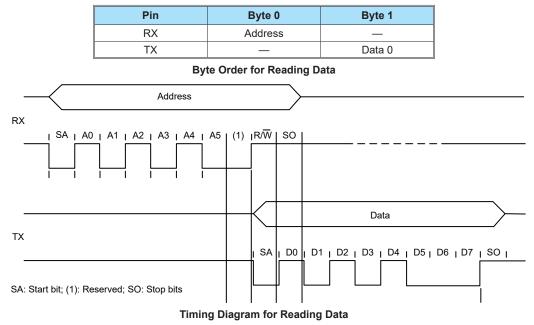

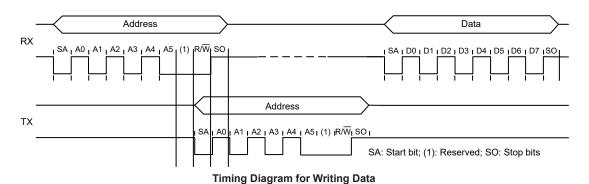

To read out data using the UART interface, the procedure shown in the following table must be used. The first sent byte defines both mode and address.

To write data using the UART interface, the procedure shown in the following table must be used. The first sent byte defines both mode and address.

| Pin | Byte 0    | Byte 1    |

|-----|-----------|-----------|

| RX  | Address 0 | Data 0    |

| TX  |           | Address 0 |

Byte Order for Writing Data

The address byte must meet the following format, as shown in the table below.

- The MSB of the first byte defines the mode.

- MSB=0 for write mode

- MSB=1 for read mode

- Bit6 is reserved.

- Bit[5:0] defines the address.

| Bit7<br>(MSB) | Bit 6    | Bit 5   | Bit4    | Bit 3   | Bit 2   | Bit 1   | Bit 0<br>(LSB) |

|---------------|----------|---------|---------|---------|---------|---------|----------------|

| 1 or 0        | Reserved | Address | Address | Address | Address | Address | Address        |

#### I<sup>2</sup>C Interface

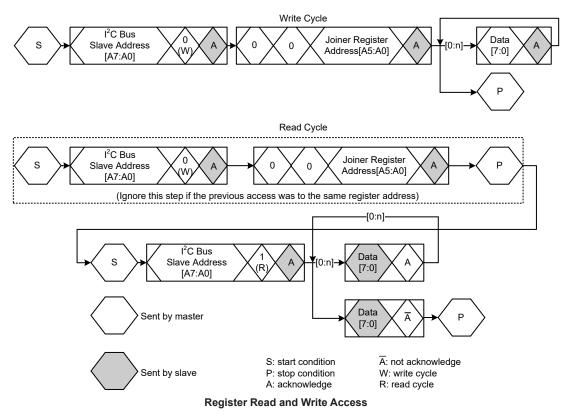

The contactless chip acts as a slave during  $I^2C$  communication and the implemented interface is inaccordance with the  $I^2C$  standard. The data transfer speed is up to 400kbit/s.

To write data from the host controller using the I<sup>2</sup>C bus, the following procedure and format must be followed:

- The first byte indicates the device address in accordance with the I<sup>2</sup>C bus standard.

- The second byte indicates the register address, followed by up to n data bytes.

- The Read/Write bit is 0.

To read data from the contactless chip using the I<sup>2</sup>C bus, the following procedure and format must be followed:

- The first byte indicates the device address in accordance with the I2C bus standard.

- The second byte indicates the register address. No data bytes are added.

- The Read/Write bit is 0.

- After the write access, read access can be started. The host sends the device address. In response, the contraceless chip sends the content of the accessed register to the host.

- The Read/Write bit is 1.

The address byte must meet the following format:

- 7-bit address setting.

- If pin EA is set to 0, the higher 4 address bits are fixed at 0101b and the lower 3 bits (ADR0, ADR1, ADR2) can be freely configured by the user.

- If pin EA is set to 1, ADR0 to ADR5 can be completely specified on the external pins by the user. ADR6 is always set to logic 0.

- The LSB defines the mode.

- LSB=0, write data to the device.

- LSB=1, read data from the device.

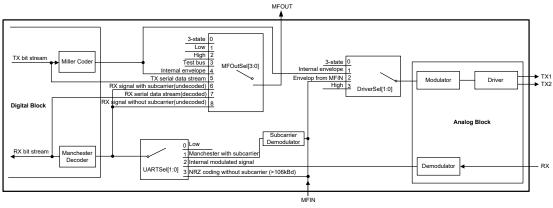

### MFIN and MFOUT Interface

The BC45B4522 is divided into a digital circuit block and an analog circuit block. The digital block contains the state machine, encoder and decoder logic circuitry, etc. The analog block contains the modulator and antenna drivers, receiver and amplifiers. The interface between these two blocks can be configured so that the interfacing signals can be routed to the MFIN and MFOUT pins. This configuration is implemented using the MFOutSel[3:0] and DriverSel[1:0] bits in the TxSel register and the UARTSel[1:0] bits in the RxSel register.

This topology allows some parts of the analog block to be connected to the digital block of another device.

The MFOutSel[3:0] bits in the TxSel register is used to measure ISO/IEC14443 A related signals. This is expecially important during the design and test phases as it enables checking of the transmitted and received data.

Pins MFOUT and MFIN can find important use in active antenna applications. An external active antenna circuit can be connected to the BC45B4522's digital block. The MFOutSel[3:0] bits must be configured to 0100b so that the internal Miller encoded signal can be sent to the MFOUT pin. The UARTSel[1:0] bits must be configured to 01b so that a Manchester signal with subcarrier is recived on the MFIN pin.

It is possible to connect a passive antenna to the TX1, TX2 and RX pins using an appropriate filter and matching circuitry, and simultaneously an active antenna to the MFIN and MFOUT pins. In this circuit configuration, two RF circuits can be driven by the same host processor.

Note that the MFIN and MFOUT pins have a dedicated power supply on pin SVDD with the ground on pin PVSS. When the MFIN pin is not used, it must be connected to either pin SVDD or pin PVSS. When the SVDD pin is not used, it must be connected to pin PVDD or any other power supply pin.

MFIN and MFOUT Signal Routing Diagram

# **Functional Description**

### **CRC Coprocessor**

The following CRC coprocessor parameters can be configured:

- The CRC preset value can be either 0000h, 6363h, A671h or FFFFh depending on the CRCPreset[1:0] setting in the Mode register.

- The CRC polynomial for the 16-bit CRC is  $X^{16} + X^{12} + X^5 + 1$ .

- The CRCResult\_H and CRCResult\_L registesrs indicate the CRC calculation result high byte and low byte respectively.

- The MSBFirst bit in the Mode register indicates that data will be loaded with the MSB first.

| Parameter           | Value                                                                                 |

|---------------------|---------------------------------------------------------------------------------------|

| CRC register length | 16-bit CRC                                                                            |

| CRC algorithm       | Algorithm according to ISO/IEC 14443 A and ITU-T                                      |

| CRC preset value    | 0000h, 6363h, A671h or FFFFh depending on CRCPreset[1:0] setting in the Mode register |

## **FIFO Buffer**

The BC45B4522 contains an  $8 \times 64$  FIFO buffer. It is used to cache the input and output data streams for communication between the host and the device internal state machine. It can manage up to 64 bytes of data streams without considering timing limitations.

### Accessing the FIFO Buffer

The FIFO buffer input and output data bus is connected to the FIFOData register. Writing to the FIFOData register will store one byte in the FIFO buffer and increase the internal FIFO buffer write pointer by 1. Reading from the FIFOData register will read the data stored in the pointed FIFO buffer and decrease the FIFO buffer read pointer by 1. The distance between the FIFO buffer write and read pointers can be obtained by reading the FIFOLevel register.

When the host controller sends a command, the BC45B4522 can access the FIFO buffer according to the command while the command is in progress. The FIFO buffer can continue to be used for input and output only when it is valid. The host controller must ensure that there are no unintentional accesses to the FIFO buffer.

### Controlling the FIFO Buffer

The FIFO buffer pointers can be reset by setting the FlushBuffer bit in the FIFOLevel register to logic 1. Consequently, the FIFOLevel[6:0] bits are all set to logic 0 and the BufferOvfl flag in the Error register is cleared to zero. In this situation, the stored bytes can no longer be accessible, allowing the FIFO buffer to store another 64 data bytes.

### **FIFO Buffer State Information**

The host device can obtain the following FIFO buffer state information:

- The number of data bytes stored in the FIFO buffer: FIFOLevel[6:0] bits in the FIFOLevel register

- FIFO buffer almost full warning: HiAlert bit in the Status1 register

- FIFO buffer almost empty warning: LoAlert bit in the Status1 register

- FIFO buffer overflow warning: BufferOvfl bit in the Error register, which can be cleared only by setting the FlushBuffer bit in the FIFOLevel register

The BC45B4522 can generate an interrupt signal when any one of the following conditions occurs:

- The LoAlertIEn bit in the ComIEn register is set to logic 1, it actives the IRQ pin when the LoAlert bit in the Status1 register changes to logic 1.

- The HiAlertIEn bit in the ComIEn register is set to logic 1, it actives the IRQ pin when the HiAlert bit in the Status1 register changes to logic 1.

- If the WaterLevel[5:0] value set in the WaterLevel register is greater than or equal to the remaining space in the FIFO buffer, the HiAlert bit is set to logic 1:

HiAlert=1 if (64-FIFOLength)≤WaterLevel

• If the WaterLevel[5:0] value set in the WaterLevel register is greater than or equal to the used space in the FIFO buffer, the LoAlert bit is set to logic 1:

$LoAlert{=}1 if FIFOLength{\leq}WaterLevel$

### Interrupt Request System

The BC45B4522 indicates various interrupt events by setting the IRq bit in the Status1 register or by activing the IRQ pin. The signal on the IRQ pin can be used to interrupt the host to use its interrupt handling capabilities. This greatly improves the efficiency of host software execution.

### Interrupt Source Overview

The following table lists the available interrupt flags, the corresoponding interrupt source and the trigger condition for their activation.

The TimerIRq interrupt flag in the ComIrq register being set high indicates an interrupt generated by the timer. When the timer decreases from 1 to 0, this flag will be set high.

The TxIRq flag in the ComIrq register being set high indicates that the transmitter sending has finished. When the state changes from sending data to sending the end of the frame, the transmitter will automatically set the corresponding interrupt flag high. The CRC coprocessor will set the CRCIRq flag high in the DivIrq register after processing all the data in the FIFO buffer which is indicated by the CRCReady bit.

The RxIRq flag in the ComIrq register being set high indicates that the end of data reception has been detected.

The IdleIRq flag in the ComIrq register will be set high if a command execution has finished and the Command[3:0] field in the Command register has changed to the Idle state.

When the HiAlert bit is set to 1 and the HiAlertIRq flag in the ComIrq register is set to 1, it indicates that the remaining space in the FIFO buffer has reached the level indicated by the WaterLevel[5:0] bits. When the LoAlert bit is set to 1 and the LoAlertIRq flag in the ComIrq register is set to 1, it indicates that the used space in the FIFO buffer has reached the level indicated by the WaterLevel[5:0] bits.

The ErrIRq flag in the ComIrq register being set high indicates that an error has been detected during the contractless UART transmission and reception. This is indicated when any bit in the Error register is set to logic 1.

The TagDetIRq flag in the DivIrq register being set high indicates that in the LPCD mode an external contractless card has been detected.

| Intrrupt Flag | Interrupt Source  | Trigger Action                                             |  |  |  |  |

|---------------|-------------------|------------------------------------------------------------|--|--|--|--|

| TimerIRq      | Timer             | The timer counts from 1 to 0                               |  |  |  |  |

| TxIRq         | Transmitter       | A data stream transmitting ends                            |  |  |  |  |

| CRCIRq        | CRC coprocessor   | All data in the FIFO buffer has been processed             |  |  |  |  |

| RxIRq         | Receiver          | A data stream receiving ends                               |  |  |  |  |

| IdleIRq       | ComIrq register   | Command execution ends                                     |  |  |  |  |

| HiAlertIRq    | FIFO buffer       | FIFO buffer is almost full                                 |  |  |  |  |

| LoAlertIRq    | FIFO buffer       | FIFO buffer is almost empty                                |  |  |  |  |

| ErrlRq        | Contractless UART | An error is detected                                       |  |  |  |  |

| TagDetIRq     | LPCD trigger      | In the LPCD mode, a card enters the atenna effective range |  |  |  |  |

### Timer Unit

The BC45B4522 has a timer unit which can be used by the external host to manage timing tasks. The timer unit can be used in one of the following timer/counter configurations:

- Time-out counter

- Watchdog counter

- Stopwatch

- Programmable one-shot trigger

- Periodic trigger

The timer unit can be used to measure the time interval between two events or to indicate the occurrence of a specified event after a certain period of time. The timer can be triggered by events explained in the following paragraphs. The timer unit does not affect any internal events, for example, a timer time-out event during data reception does not affect the automatic processing of this process. In addition, several timer-related bits can be used to generate an interrupt.

The timer has an input clock of 13.56MHz, which is obtained by dividing the frequency of a 27.12MHz quartz crystal oscillator. The timer consists of two stages: prescaler and counter.

The prescaler (TPrescaler) is a 12-bit counter, which is set using the TPrescaler\_Hi[3:0] bits in the TMode register and the TPrescaler\_Lo[7:0] bits in the TPrescaler register. The 16-bit reload value for the counter, TReloadVal, can be set between 0 and 65535 using the TReload\_H and TReload\_L registers. The current value of the timer is indicated in the TCouterVal\_H and TCouterVal\_L registers.

When the counter value reaches 0, an interrupt is automatically generated, which is indicated by the TimerIRq flag in the ComIrq register. If enabled, this interrupt signal can be indicated on the IRQ pin. The TimerIRq flag can be set and reset by the host. Depending on the configuration, the timer can stop at 0 or restart with the value set in the TReload\_H and TReload\_L registers.

The timer status is indicated by the TRunning bit in the Status1 register.

The timer can be started using the TStartNow bit in the Control register and stopped using the TStopNow bit in the same register.

To meet some specific protocol requirements, the timer can also be activated automatically by setting the TAuto bit

in the TMode register to logic 1.

The delay time of a timing process is set by the reload value plus one. The total delay time is calculated using the following equation:

$t_d = (TPrescaler \times 2+1) \times (TReloadVal+1) \div 13.56MHz$

An example of calculating the total delay time is shown below, where TPrescaler=4095 and TReloadVal=65535:

39.59s=(4095×2+1)×(65535+1)÷13.56MHz

For example, a delay unit of 25µs requires 339 timer clock cycles to be counted and a TPrescaler value of 169. This configuration allows the timer to count every 25µs up to 65535 times.

### LPCD Unit

The LPCD is the abbreviation of Low Power external Card Detection. This function allows the device to detect whether an external contactless card is close to it with a very low standby power consumption. If an card has been detected, an interrupt can be output to inform the host MCU to enter the normal reader communication mode and implement data exchange with the card.

### LPCD Operating Principle

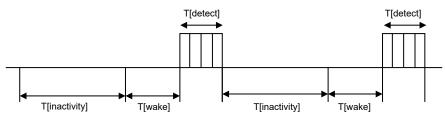

The LPCD mode is divided into three stages, T[inactivity](sleep period), T[wake](active period) and T[detect] (detection period), acorresponding to different actions, as shown below.

In the initial state, the chip detects the antenna field strength in the current field and automatically records it. When a card is within the effective range of the antenna, it will cause the antenna field strength to change beyond the Delta[3:0] value in the LPCD register, then the chip will automatically change to the reader state and trigger the TagDetIRq interrupt. The LPCD function related registers include the LPCD, WUPeriod and SwingsCnt.

The LPCD time parameters are described below:

- Sleep period: T[inactivity]=WUPeriod[7:0]  $\times$  256  $\times$  Tclk\_32k

- Active period: T[wake]=400µs (Typ.)

- Detection period: T[detect]=SwingsCnt[3:0]  $\times$  16  $\times$  4  $\times$  Tclk\_27M12

- Card detection total time=(T[inactivity] + T[wake] + T[detect] × (Skip[2:0] + 1)

### TX Driver

The signals on the TX1 and TX2 pins are signals modulated by a 13.56MHz carrier, which can be used to directly drive an antenna with some passive components for matching and filtering.

The signals on the TX1 and TX2 pins can be configured using the TxControl register. The modulation index can be set by adjusting the impedance of the driver so as to adjust the output power, current consumption and operating distance. The impedance of the P driver is configured using the CWGsP and ModGsP registers. The impedance of the N driver is configured using the GsN register. The modulation index also depends on antenna design and tunning.

### **Power Saving Modes**

### Hardware Power-down

The hardware power-down mode is enabled when the NRSTPD pin is pulled low. This mode turns off all internal current sinks including the oscillator. All digital input buffers are separated from the input pins and their functionality is turned off (except pin NRSTPD). The output pins remain at either a high or low level.

#### Software Power-down

The software power-down mode is entered immediately after the PowerDown bit in the Command register is set to logic 1. This mode turns off all internal current sinks including the oscillator buffer. However, the digital input buffers are not separated from the input pins and remain their functionality. The status of the digital output pins remains unchanged.

During the software power-down, all register values, FIFO buffer content and configuration remain unchanged.

After setting the PowerDown bit to logic 0, it takes 1024 clocks to exit the software power-down mode. Setting the PowerDown bit low does not immediately clear it. This bit is cleared automatically by the chip when the software power-down mode is exited.

#### **Transmitter Power-down**

The transmitter power-down mode turns off the internal antenna drivers, thereby switching off the RF field. The transmitter power-down mode is entered by setting the TxRFEn bit in the TxControl register to 00b.

### **Oscillator Circuit**

The clock applied to the BC45B4522 provides a time basis for the encoder and decoder synchronized to the system. Therefore, the stability of the clock frequency is an important factor to ensure the good performance of the system. To achieve the best performance, clock jitter must be as minimized.

# Registers

### **Register Bit Behavior**

Depending on the functionality of the register, the access conditions of the registers are also different. The following table describes different access conditions for the registers.

| Abbreviation | Behavior   | Description                                                                                                                                                                                                                                                                                                                         |

|--------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W          | Read/Write | These bits can be read and written by the host controller. Since they are used only for control, their contents are not affected by the internal state machine. For example, the ComIEn register can be read and written by the host controller, but it can only be read by the internal state machine and cannot be changed by it. |

| D            | Dynamic    | These bits can be read and written by the host controller. They can also be written automatically by the internal state machine. For example, the Command register automatically changes the value of certain bits in it after command execution.                                                                                   |

| W            | Write only | Reading these register bits always returns zero.                                                                                                                                                                                                                                                                                    |

| R            | Read only  | These registser bits are determined by the internal states only.                                                                                                                                                                                                                                                                    |

| Reserved     | —          | These register bits are reserved for future use and cannot be changed.                                                                                                                                                                                                                                                              |

### **Register Overview**

To access the registers of pages 4~6, the PageSel register of page 3 should first be configured to the correct switch value before executing any operations to the registers in the corresponding page.

| Address | Deviator      | <b>F</b> unction                                    |

|---------|---------------|-----------------------------------------------------|

| (Hex)   | Register Name | Function                                            |

| Page 0  |               |                                                     |

| 00h     | Reserved      | _                                                   |

| 01h     | Command       | Start and stop command execution                    |

| 02h     | ComIEn        | Interrupt request enable or disable control bits    |

| 03h     | DivlEn        | Interrupt request enable or disable control bits    |

| 04h     | Comlrq        | Interrupt request bits                              |

| 05h     | Divlrq        | Interrupt request bits                              |

| 06h     | Error         | Error status of the last command executed           |

| 07h     | Status1       | Communication status bits                           |

| 08h     | Status2       | Receiver and transmitter status bits                |

| 09h     | FIFOData      | 64-byte FIFO buffer input/output                    |

| 0Ah     | FIFOLevel     | Number of bytes stored in the FIFO buffer           |

| 0Bh     | WaterLevel    | Level for FIFO buffer overflow and empty warning    |

| 0Ch     | Control       | Internal controller                                 |

| 0Dh     | BitFraming    | Adjustment for bit-oriented frames                  |

| 0Eh     | Coll          | Bit position of the first bit-collision detected    |

| Page 1  | ·             |                                                     |

| 10h     | Reserved      | _                                                   |

| 11h     | Mode          | General mode setting for transmitting and receiving |

| 12h     | TxMode        | Transmission data rate and frame format             |

| 13h     | RxMode        | Reception data rate and frame format                |

| 14h     | TxControl     | Antenna driver pins TX1 and TX2 control             |

| 15h     | TxASK         | Transmission modulation settings                    |

| 16h     | TxSel         | Antenna driver signal source selection              |

| 17h     | RxSel         | Internal receiver settings                          |

| 18h     | Reserved      | _                                                   |

| 19h     | Demod         | Demodulation settings                               |

17

| Address Begister Name |               | Function                                                                                       |  |  |  |  |  |

|-----------------------|---------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

| (Hex)                 | Register Name | Function                                                                                       |  |  |  |  |  |

| 1Ch                   | MfTx          | Transmission waiting time control                                                              |  |  |  |  |  |

| 1Dh                   | MfRx          | Parity function and high-pass bandwidth settings                                               |  |  |  |  |  |

| 1Eh                   | ТуреВ         | ISO/IEC 14443 B control                                                                        |  |  |  |  |  |

| 1Fh                   | SerialSpeed   | Serial UART data rate selection                                                                |  |  |  |  |  |

| Page 2                | 1             |                                                                                                |  |  |  |  |  |

| 20h                   | Reserved      | _                                                                                              |  |  |  |  |  |

| 21h                   | CRCResult_H   | CRC result high byte                                                                           |  |  |  |  |  |

| 22h                   | CRCResult_L   | CRC result low byte                                                                            |  |  |  |  |  |

| 23h                   | Reserved      | _                                                                                              |  |  |  |  |  |

| 24h                   | ModWidth      | Modulation width control                                                                       |  |  |  |  |  |

| 25h                   | Reserved      | _                                                                                              |  |  |  |  |  |

| 26h                   | RFCfg         | Receiver gain setting                                                                          |  |  |  |  |  |

| 27h                   | GsN           | Controls the conductance of N driver output during non-modulation period and modulation period |  |  |  |  |  |

| 28h                   | CWGsP         | Controls the conductance of P driver output during non-modulation period                       |  |  |  |  |  |

| 29h                   | ModGsP        | Controls the conductance of P driver output during modulation period                           |  |  |  |  |  |

| 2Ah                   | TMode         |                                                                                                |  |  |  |  |  |

| 2Bh                   | TPrescaler    | Internal timer settings                                                                        |  |  |  |  |  |

| 2Ch                   | TReload_H     | 16-bit timer reload value high byte                                                            |  |  |  |  |  |

| 2Dh                   | TReload_L     | 16-bit timer reload value low byte                                                             |  |  |  |  |  |

| 2Eh                   | TCounterVal_H | 16-bit timer current value high byte                                                           |  |  |  |  |  |

| 2Fh                   | TCounterVal_L | 16-bit timer current value low byte                                                            |  |  |  |  |  |

| Page 3                | 1             |                                                                                                |  |  |  |  |  |

| 33h                   | TestPinEn     | Programmable I/O (D1-D6) enable bits                                                           |  |  |  |  |  |

| 34h                   | TestPinValue  | Programmable I/O (D1-D6) control bits                                                          |  |  |  |  |  |

| 37h                   | PageSel       | Controls the register page switching                                                           |  |  |  |  |  |

| Page 4                |               |                                                                                                |  |  |  |  |  |

| 31h                   | TestSel       | MFOUT output signal selection                                                                  |  |  |  |  |  |

| 32h                   | DataPullD     | Pull-high control for MFIN and programmable I/O                                                |  |  |  |  |  |

| 33h                   | RxAlgorithm0  | Demodulation algorithm adjustment                                                              |  |  |  |  |  |

| 34h                   | AGCCfg0       | Automatic gain control bits                                                                    |  |  |  |  |  |

| 35h                   | AGCCfg1       | Automatic gain control bits                                                                    |  |  |  |  |  |

| 36h                   | RxAlgorithm1  | Demodulation algorithm adjustment                                                              |  |  |  |  |  |

| 38h                   | RxAlgorithm2  | Demodulation algorithm adjustment                                                              |  |  |  |  |  |

| 39h                   | RxAlgorithm3  | Demodulation algorithm adjustment                                                              |  |  |  |  |  |

| 3Ah                   | RxCK          | TypeA waveform falling time adjustment; phase selection                                        |  |  |  |  |  |

| 3Bh                   | RxBand        | Signal-to-noise ratio adjustment                                                               |  |  |  |  |  |

| 3Ch                   | LPCD          | LPCD control bits                                                                              |  |  |  |  |  |

| 3Dh                   | WUPeriod      | LPCD sleep time setting                                                                        |  |  |  |  |  |

| 3Eh                   | SwingsCnt     | LPCD enable; LPCD detection time setting                                                       |  |  |  |  |  |

| 3Fh                   | Special       | Receiver demodulation control                                                                  |  |  |  |  |  |

| Page 5                |               |                                                                                                |  |  |  |  |  |

| 31h                   | Analog        | High temperature protection control bits                                                       |  |  |  |  |  |

| 32h                   | Noise         | Noise threshold control bits                                                                   |  |  |  |  |  |

| 33h                   | StepCtrl      | Transmitter modulation control bits                                                            |  |  |  |  |  |

| 34h                   | AgcMin        | AGC amplitude threshold setting                                                                |  |  |  |  |  |

| 38h                   | RxAlgorithm6  | Demodulation algorithm adjustment                                                              |  |  |  |  |  |

| Address | Deviator Norra | Function                              |  |  |  |  |  |

|---------|----------------|---------------------------------------|--|--|--|--|--|

| (Hex)   | Register Name  | Function                              |  |  |  |  |  |

| 39h     | RxAlgorithm7   | Demodulation algorithm adjustment     |  |  |  |  |  |

| 3Ah     | RxAlgorithm8   | Demodulation algorithm adjustment     |  |  |  |  |  |

| 3Bh     | RxAlgorithm9   | Demodulation algorithm adjustment     |  |  |  |  |  |

| Page 6  |                |                                       |  |  |  |  |  |

| 31h     | LPCDRef        | LPCD reference value                  |  |  |  |  |  |

| 32h     | LPCDDet        | LPCD detected value                   |  |  |  |  |  |

| 33h     | Calibration    | LPCD calibration control bits         |  |  |  |  |  |

| 34h     | RC27MCalValue  | LPCD 27.12MHz clock calibration value |  |  |  |  |  |

| 35h     | RC32KCalValue  | LPCD 32kHz clock calibration value    |  |  |  |  |  |

| 36h     | LPCDADCRef     | LPCD ADC reference level              |  |  |  |  |  |

| 38h     | CWGsN_LPCD     | LPCD N driver control                 |  |  |  |  |  |

| 39h     | CWGsP_LPCD     | LPCD P driver control                 |  |  |  |  |  |

### **Register Description**

#### **Public Registesr description**

#### Page 0

#### Command Register

Start and stop command execution.

| Address | Bit                     | 7           | 6           | 5           | 4                              | 3            | 2  | 1 | 0 |

|---------|-------------------------|-------------|-------------|-------------|--------------------------------|--------------|----|---|---|

|         | Name                    | Rese        | erved       | RcvOff      | PowerDown                      | Command[3:0] |    |   |   |

| 01h     | Туре                    | F           | र           | R/W         | R/W                            |              | R/ | W |   |

|         | Reset Value             | 0           | 0           | 1           | 0                              | 0            | 0  | 0 | 0 |

| Bit 7~6 | Reserved: Reserved bits |             |             |             |                                |              |    |   |   |

| Bit 5   | RcvOff: Re              | eceiver ana | log block o | n/off contr | ol                             |              |    |   |   |

|         | 0: On                   |             |             |             |                                |              |    |   |   |

|         | 1: Off                  |             |             |             |                                |              |    |   |   |

| Bit 4   | PowerDow                | n: Softwar  | e power-do  | own mode    | control                        |              |    |   |   |

|         | 0: Chip i               | n ready sta | te          |             |                                |              |    |   |   |

|         | 1: Chip e               | enters powe | er-down mo  | ode         |                                |              |    |   |   |

| Bit 3~0 | Command                 | [3:0]: Com  | mand cont   | rol         |                                |              |    |   |   |

|         |                         |             | ,           |             | sponding com<br>Refer to the C |              |    | 0 |   |

### ComlEn Register

Interrupt enable and disable control bits.

| Address | Bit         | 7      | 6     | 5     | 4       | 3          | 2          | 1      | 0        |

|---------|-------------|--------|-------|-------|---------|------------|------------|--------|----------|

|         | Name        | lRqInv | TxlEn | RxIEn | ldlelEn | HiAlertIEn | LoAlertIEn | ErrlEn | TimerlEn |

| 02h     | Туре        | R/W    | R/W   | R/W   | R/W     | R/W        | R/W        | R/W    | R/W      |

|         | Reset Value | 1      | 0     | 0     | 0       | 0          | 0          | 0      | 0        |

Bit 7

**IRqInv**: IRQ pin state non-inverting/inverting with IRq bit state (Status1 register) control 0: Non-invert

1: Invert

In combination with the IRQPushPull bit in the DivIEn register, the default vlaue of logic 1 ensures that the output level on the IRQ pin is 3-state.

| Bit 6 | <b>TxIEn</b> : Send TxIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed       |

|-------|----------------------------------------------------------------------------------------------|

| Bit 5 | <b>RxIEn</b> : Send RxIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed       |

| Bit 4 | IdleIEn: Send IdleIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed           |

| Bit 3 | HiAlertIEn: Send HiAlertIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed     |

| Bit 2 | LoAlertIEn: Send LoAlertIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed     |

| Bit 1 | ErrIEn: Send ErrIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed             |

| Bit 0 | <b>TimerIEn</b> : Send TimerIRq interrupt request to IRQ pin<br>0: Not allowed<br>1: Allowed |

### DivlEn Register

Interrupt enable and disable control bits.

| Type<br>Set Value<br>RQPushPu<br>0: Open-dr<br>1: Standard<br>eserved: R<br>ngDetIEn: | R/W<br>0<br>all: IRQ output<br>rain output<br>d CMOS outp<br>Leserved bit<br>Send TagDet      | put                                                                                                                                                        | TagDetlEn<br>R/W<br>0                                                                                                                                                              | MfinActIEn<br>R/W<br>0                                                                                                                                                                                    | Reserved<br>—<br>0                                                                                                                                                                                | CRCIEn<br>R/W<br>0                                                                                                                                                                                | Rese<br>–<br>0                                                                                                                                                                                    | erved<br>                                                                                                                                                                                                                  |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| QPushPu<br>0: Open-dr<br>1: Standard<br>eserved: R<br>ngDetIEn:                       | 0<br>Ill: IRQ outpu<br>rain output<br>d CMOS outp<br>Leserved bit<br>Send TagDet              | ut control                                                                                                                                                 | 0                                                                                                                                                                                  | 0                                                                                                                                                                                                         | 0                                                                                                                                                                                                 |                                                                                                                                                                                                   | 0                                                                                                                                                                                                 | 0                                                                                                                                                                                                                          |  |

| Type         R/W         R/W         R/W         R/W                                  |                                                                                               | 0                                                                                                                                                          | 0                                                                                                                                                                                  |                                                                                                                                                                                                           |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |  |

| 0: Open-di<br>1: Standard<br>eserved: R<br>ngDetIEn:                                  | rain output<br>ed CMOS outp<br>ceserved bit<br>Send TagDet                                    | put                                                                                                                                                        | upt request t                                                                                                                                                                      | R/W   —   R/W   —     0   0   0   0     o   IRQ pin                                                                                                                                                       |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |  |

| gDetIEn:                                                                              | Send TagDet                                                                                   | tIRq interru                                                                                                                                               | upt request t                                                                                                                                                                      | o IRQ pin                                                                                                                                                                                                 |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |  |

|                                                                                       |                                                                                               | tIRq interru                                                                                                                                               | upt request t                                                                                                                                                                      | o IRQ pin                                                                                                                                                                                                 |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |  |

| 0: Not allowed                                                                        |                                                                                               |                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                                                                                                           |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |  |

| MfinActIEn: Send MfinActIRq interrupt request to IRQ pin<br>0: Not allowed            |                                                                                               |                                                                                                                                                            |                                                                                                                                                                                    |                                                                                                                                                                                                           |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                   |                                                                                                                                                                                                                            |  |