# **CAN Bus Controller**

# HT45B3305H/HT45B3315

Revision: V1.40 Date: June 19, 2024

www.holtek.com

# **Table of Contents**

| Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4                                                                                                                          |

| General Description                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4                                                                                                                          |

| Selection Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5                                                                                                                          |

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5                                                                                                                          |

| Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                                                          |

| Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                                                                                          |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                                                          |

| D.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                          |

| Operating Voltage Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                                          |

| Operating Current Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                                                                          |

| Standby Current Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8                                                                                                                          |

| A.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                                                                                                                          |

| System Frequency Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8                                                                                                                          |

| Timing Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                                                                                                                          |

| CAN Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                                                                                                                          |

| Power-on Reset Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                            |

| Power Control Function                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10                                                                                                                         |

| Power Control Function<br>External Crystal Oscillator – HXT                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                                         |

| External Crystal Oscillator – HXT                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10<br>10                                                                                                                   |

| External Crystal Oscillator – HXT<br>CLKOUT Pin                                                                                                                                                                                                                                                                                                                                                                                                                                | 10<br>10<br>11                                                                                                             |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode                                                                                                                                                                                                                                                                                                                                                                                                                   | 10<br>10<br>11<br>11                                                                                                       |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description<br>Write Buffer and Data Check.                                                                                                                                                                                                                                                                                                                               |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description<br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface                                                                                                                                                                                                                         |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br><b>Functional Description</b><br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields.<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram                                                                                                                                                                       |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description<br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins                                                                                                                                                      |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description<br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins<br>Message RAM and FIFO Buffer Configuration                                                                                                         |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description<br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins<br>Message RAM and FIFO Buffer Configuration<br>HT45B3305H/HT45B3315 CAN Operating Modes                                                             | 10<br>10<br>11<br>11<br>11<br>12<br>12<br>13<br>13<br>16<br>17<br>19<br>20<br>20<br>20<br>22                               |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br><b>Functional Description</b><br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins<br>Message RAM and FIFO Buffer Configuration<br>HT45B3305H/HT45B3315 CAN Operating Modes<br>CAN Application                                   | 10<br>10<br>11<br>11<br>11<br>12<br>12<br>13<br>16<br>17<br>19<br>20<br>20<br>20<br>22<br>25                               |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br><b>Functional Description</b><br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields.<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins<br>Message RAM and FIFO Buffer Configuration<br>HT45B3305H/HT45B3315 CAN Operating Modes<br>CAN Application<br><b>Register Description</b> . |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br>Functional Description<br>Write Buffer and Data Check<br>SPI and I <sup>2</sup> C Frame Fields<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins<br>Message RAM and FIFO Buffer Configuration<br>HT45B3305H/HT45B3315 CAN Operating Modes<br>CAN Application<br>Register Description<br>Register Map   |                                                                                                                            |

| External Crystal Oscillator – HXT<br>CLKOUT Pin<br>IDLE Mode<br>SLEEP Mode and Wake-up<br><b>Functional Description</b><br>Write Buffer and Data Check.<br>SPI and I <sup>2</sup> C Frame Fields.<br>SPI Serial Interface<br>I <sup>2</sup> C Serial Interface<br>HT45B3305H/HT45B3315 CAN Block Diagram<br>Interrupt Output Pins<br>Message RAM and FIFO Buffer Configuration<br>HT45B3305H/HT45B3315 CAN Operating Modes<br>CAN Application<br><b>Register Description</b> . | 10<br>10<br>11<br>11<br>11<br>12<br>12<br>13<br>16<br>16<br>17<br>19<br>20<br>20<br>20<br>20<br>22<br>25<br>33<br>33<br>33 |

| Application Circuits                    | 59                                      |

|-----------------------------------------|-----------------------------------------|

| SPI Serial Interface                    |                                         |

| I <sup>2</sup> C Serial Interface       | 60                                      |

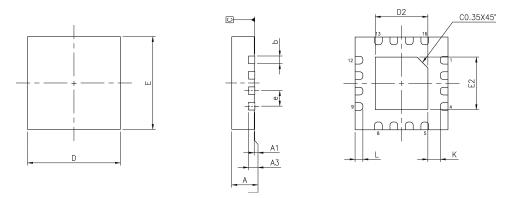

| Package Information                     | 61                                      |

| rackage information                     | ••••••••••••••••••••••••••••••••••••••• |

| 16-pin NSOP (150mil) Outline Dimensions |                                         |

# **Features**

- Operating Voltage: 3.0V~5.5V

- Oscillator Type: High Speed External Crystal HXT

- Sleep Mode and Idle Mode

- 32-byte Write Buffer with Data Check Unit for communicating with Host MCUs

- Serial Communication Interfaces I<sup>2</sup>C or SPI (up to 10MHz SPI data rate)

- For HT45B3305H only, in order to ensure correct data transmission, the SPI and I<sup>2</sup>C interfaces cannot be used in one(master MCU)-to-multiple(slave devices) situations

- Clock Out pin with programmable prescaler

- Interrupt output pins with selectable active level configuration

- HT45B3305H/HT45B3315 CAN Core, contains the following features:

- Conforms to ISO11898-1 and CAN 2.0A/B

- 32 Message Objects

- Each Message Object has its own identifier mask

- Programmable FIFO mode concatenation of Message Objects

- Maskable interrupt

- Programmable loop-back mode for self-test operation

- Support the SOF (Start of Frame) signal output

- 32×139-bit Message Memory

- Package types: 16-pin NSOP/QFN

# **Applications**

- Networked Automotive Products

- Industrial Automation

- Entertainment Products

# **General Description**

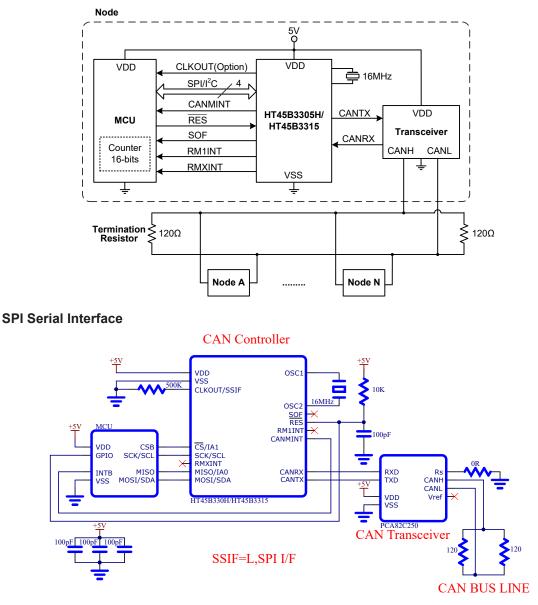

A complete CAN Node requires a CAN controller, a CAN transceiver and a microcontroller.

The devices are developed as stand-alone CAN (Controller Area Network) controllers. For the connection to the physical layer additional transceiver hardware is required. Two pins of CANTX and CANRX interface to the CAN BUS Transceiver. The devices include a SPI and I<sup>2</sup>C interfaces to communicate with a microcontroller.

The HT45B3305H/HT45B3315 CAN Module licensed from Bosch. The HT45B3305H/HT45B3315 CAN supports the CAN 2.0 Part A and B protocol specifications and compatible with the ISO11898-1 standards. This CAN Module abbreviated as C\_CAN. It is capable of transmitting and receiving standard and extended messages. It also capable of both acceptance filtering and message handler and includes 32 Message Objects which can be concatenated to configurate FIFO buffer with different depth. The SPI interface with data rate of up 10MHz and I<sup>2</sup>C serial interface are provided for communication with a SPI or I<sup>2</sup>C based 8-bit MCU.

# **Selection Table**

| Part No.   | VDD       | Max. Freq. | Protocol                 | Message<br>Objects | Temperature Rage | Interface          | Package         |

|------------|-----------|------------|--------------------------|--------------------|------------------|--------------------|-----------------|

| HT45B3305H | 3.0V~5.5V | 24MHz      | CAN 2.0A/B<br>ISO11898-1 | 32                 | -40°C~125°C      | CAN×1<br>SPI/I²C×1 | 16NSOP<br>16QFN |

| HT45B3315  | 3.0V~5.5V | 24MHz      | CAN 2.0A/B<br>ISO11898-1 | 32                 | -40°C~105°C      | CAN×1<br>SPI/I²C×1 | 16NSOP<br>16QFN |

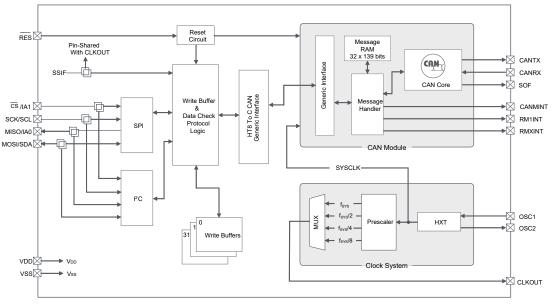

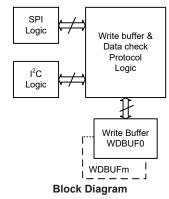

# **Block Diagram**

: Pin-Shared Node

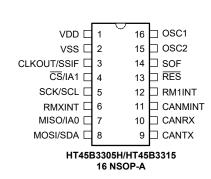

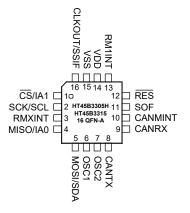

# **Pin Assignment**

# **Pin Description**

| Pin Name    | Function | Туре | Description                                                                                                           |

|-------------|----------|------|-----------------------------------------------------------------------------------------------------------------------|

| CLKOUT/SSIF | CLKOUT   | 0    | Clock output pin with programmable prescaler                                                                          |

| CLKOU1/SSIF | SSIF     | I    | SPI or I <sup>2</sup> C interface selection pin when $\overline{\text{RES}}$ was low                                  |

| CS/IA1      | CS       | I    | Chip Select input pin for SPI interface                                                                               |

| CS/IAT      | IA1      | Ι    | Define I <sup>2</sup> C address bit 1 when RES was low                                                                |

| SCK/SCL     | SCK      | Ι    | Clock input pin for SPI interface                                                                                     |

| SCRIGE      | SCL      | I    | Clock input pin for I <sup>2</sup> C interface                                                                        |

| MISO/IA0    | MISO     | 0    | Master In Slave Out, the device data output for SPI interface                                                         |

| MISO/IA0    | IA0      | Ι    | Defining I <sup>2</sup> C address bit 0 when $\overline{\text{RES}}$ was low                                          |

| MOSI/SDA    | MOSI     | Ι    | Master Out Slave In, the device data input for SPI interface                                                          |

| 1003/3DA    | SDA      | I/O  | Data input/output for I <sup>2</sup> C interface                                                                      |

| OSC1        | OSC1     | I    | Oscillator input                                                                                                      |

| OSC2        | OSC2     | 0    | Oscillator output                                                                                                     |

| SOF         | SOF      | 0    | Start of Frame signal                                                                                                 |

| RES         | RES      | I    | Reset input, active-low                                                                                               |

| CANMINT     | CANMINT  | 0    | CAN Interrupt output pin                                                                                              |

| RM1INT      | RM1INT   | 0    | Receive a Message into Message Object 1 Successfully Interrupt                                                        |

| RMXINT      | RMXINT   | 0    | Receive a Message into Message Object x Successfully Interrupt, the x value is user-defined using the CANCFG Register |

| CANTX       | CANTX    | 0    | Transmit output pin to CAN bus                                                                                        |

| CANRX       | CANRX    | Ι    | Receive input pin from CAN bus                                                                                        |

| VDD         | VDD      | PWR  | Digital positive power supply.                                                                                        |

| VSS         | VSS      | PWR  | Ground                                                                                                                |

Legend: I= Input; O= Output; PWR= Power

# **Absolute Maximum Ratings**

| Supply VoltageVss-0.3V to 6                  | .0V |

|----------------------------------------------|-----|

| Input Voltage                                | .3V |

| Storage Temperature60°C to 150               | 0°C |

| Operating Temperature (HT45B3305H)40°C to 12 | 5°C |

| Operating Temperature (HT45B3315)40°C to 10  | 5°C |

| l <sub>oL</sub> Total                        | mА  |

| loн Total80                                  | mA  |

| Fotal Power Dissipation                      | nW  |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the devices. Functional operation of these devices at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

# D.C. Characteristics

For data in the following tables, note that factors such as oscillator type, operating voltage, operating frequency, pin load conditions, temperature and program instruction type, etc., can all exert an influence on the measured values.

# **Operating Voltage Characteristics**

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified. For HT45B3315: Ta=-40°C~105°C, unless otherwise specified.

| Symbol | Devenueter              |     | Test Conditions                           | Min  | Тур. | Max. | 11   |

|--------|-------------------------|-----|-------------------------------------------|------|------|------|------|

|        | Parameter               | VDD | Conditions                                | Min. |      |      | Unit |

|        | Operating Voltage (HXT) | _   | f <sub>sys</sub> =f <sub>HXT</sub> =8MHz  | 3.0  | _    | 5.5  | V    |

| VDD    |                         |     | f <sub>sys</sub> =f <sub>HXT</sub> =16MHz | 3.0  | _    | 5.5  | V    |

|        |                         |     | f <sub>sys</sub> =f <sub>HXT</sub> =24MHz | 4.5  |      | 5.5  | V    |

# **Operating Current Characteristics**

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified. For HT45B3315: Ta=-40°C~105°C, unless otherwise specified

| Symbol | Parameter                                                                |      | Test Conditions                           | Min.               | True | Max.            | Unit |

|--------|--------------------------------------------------------------------------|------|-------------------------------------------|--------------------|------|-----------------|------|

| Symbol | Parameter                                                                | VDD  | Conditions                                | wiin.              | Тур. | wax.            | Unit |

|        |                                                                          | 3V   | No load, all peripherals off,             | _                  | 8    | 13              | mA   |

|        |                                                                          | 5V   | f <sub>sys</sub> =f <sub>HXT</sub> =8MHz  | —                  | 13   | 18              | mA   |

| IDD    | Operating Current<br>(HXT)                                               | 3V   | No load, all peripherals off,             |                    | 15   | 20              | mA   |

|        |                                                                          | 5V   | f <sub>sys</sub> =f <sub>HXT</sub> =16MHz | —                  | 25   | 30              | mA   |

|        |                                                                          | 4.5V | No load, all peripherals off,             | —                  | 23   | 28              | mA   |

|        |                                                                          | 5V   | f <sub>sys</sub> =f <sub>Hxt</sub> =24MHz |                    | 38   | 41              | mA   |

| VIL    | Input Low Voltage for<br>SSIF/CS/SCK/SCL/MOSI/SDA/IA0/<br>IA1/CANRX Pins | _    | _                                         | 0                  | —    | $0.2V_{DD}$     | V    |

|        | Input Low Voltage for RES Pin                                            | _    | _                                         | 0                  | _    | $0.4V_{DD}$     | V    |

| VIH    | Input High Voltage for SSIF/CS/SCK/<br>SCL/MOSI/SDA/IA0/IA1/CANRX Pins   | _    | _                                         | 0.8V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |

|        | Input High Voltage for RES Pin                                           | —    | _                                         | $0.9V_{\text{DD}}$ | _    | V <sub>DD</sub> | V    |

| lo     | Sink Current for MISO/SDA/RMXINT/<br>RM1INT/CANMINT/CLKOUT/SOF/          | 3V   | $V_{OL} = 0.1 V_{DD}$                     | 4                  | 8    |                 | mA   |

|        | CANTX Pins                                                               | 5V   |                                           | 10                 | 20   | —               | mA   |

| Іон    |                                                                          | 3V   | VoH=0.9Vpp                                | -2                 | -4   | —               | mA   |

| IOH    | RMXINT/RM1INT/CANMINT/CLKOUT/<br>SOF/CANTX Pins                          |      | VOH-0.3VDD                                | -5                 | -10  | _               | mA   |

# **Standby Current Characteristics**

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified.

| Symbol           | Parameter                          |                 | Test Conditions                                                         | Min | Тур. | Mox  | Max.  | Max.   | Max.   | Unit |

|------------------|------------------------------------|-----------------|-------------------------------------------------------------------------|-----|------|------|-------|--------|--------|------|

| Symbol           | Farameter                          | $V_{\text{DD}}$ | D Conditions                                                            |     | Typ. | Wax. | @85°C | @105°C | @125°C | onit |

|                  |                                    | 3V              | No load all paripharala off                                             |     | —    | 1    | 1     | 3      | 5      | μA   |

|                  | (SLEEP mode)                       | 5V              | No load, all peripherals off                                            |     | -    | 2    | 2     | 5      | 8      | μA   |

|                  |                                    | 3V              | No load, all peripherals off, $f_{\text{SYS}} = f_{\text{HXT}} = 8 MHz$ | _   | —    | 1    | 1     | 1      | 1      | mA   |

|                  |                                    | 5V              |                                                                         |     | _    | 1.5  | 1.5   | 1.5    | 1.5    | mA   |

| I <sub>STB</sub> | Standby Current                    | 3V              | No load, all peripherals off,                                           |     | —    | 1.2  | 1.2   | 1.2    | 1.2    | mA   |

|                  | (IDLE mode)                        | 5V              | f <sub>sys</sub> =f <sub>HXT</sub> =16MHz                               |     | _    | 2.2  | 2.2   | 2.2    | 2.2    | mA   |

|                  | 4.5V No load, all peripherals off, |                 | —                                                                       | 1.8 | 1.8  | 1.8  | 1.8   | mA     |        |      |

|                  | 5V                                 |                 | f <sub>SYS</sub> =f <sub>HXT</sub> =24MHz                               |     | _    | 2.8  | 2.8   | 2.8    | 2.8    | mA   |

For HT45B3315: Ta=-40°C~105°C, unless otherwise specified.

| Symbol | Parameter       |      | Test Conditions                           | Min  | Tur  | Max  | Max.  | Max.   | Unit |

|--------|-----------------|------|-------------------------------------------|------|------|------|-------|--------|------|

| Symbol | Parameter       | VDD  | Conditions                                | Min. | Тур. | Max. | @85°C | @105°C | Unit |

|        | Standby Current | 3V   | No load all paripharals off               |      | _    | 1.0  | 1.0   | 1.5    | μA   |

|        | (SLEEP mode)    | 5V   | No load, all peripherals off              | _    | _    | 1.5  | 1.5   | 2.5    | μA   |

|        | _               | 3V   | No load, all peripherals off,             | —    | —    | 2.0  | 2.0   | 3.5    | mA   |

|        |                 | 5V   | f <sub>SYS</sub> =f <sub>HXT</sub> =8MHz  | _    | _    | 2.5  | 2.5   | 4.5    | mA   |

| ISTB   | Standby Current | 3V   | No load, all peripherals off,             | _    | _    | 2.0  | 2.0   | 2.5    | mA   |

|        | (IDLE mode)     | 5V   | f <sub>sys</sub> =f <sub>Hxt</sub> =16MHz | _    | _    | 3.5  | 3.5   | 4.5    | mA   |

|        |                 | 4.5V | No load, all peripherals off,             | _    | _    | 3.5  | 3.5   | 4.0    | mA   |

|        | 5               | 5V   | f <sub>SYS</sub> =f <sub>HXT</sub> =24MHz |      | _    | 4.5  | 4.5   | 5.0    | mA   |

# A.C. Characteristics

For data in the following tables, note that factors such as oscillator type, operating voltage, operating frequency and temperature etc., can all exert an influence on the measured values.

# System Frequency Characteristics

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified. For HT45B3315: Ta=-40°C~105°C, unless otherwise specified.

| Symbol           | Deremeter          | Те              | st Conditions                             | Min.  | Turn | Max.  | l lm if |

|------------------|--------------------|-----------------|-------------------------------------------|-------|------|-------|---------|

|                  | Parameter          | V <sub>DD</sub> | Conditions                                | wiin. | Тур. | WidX. | Unit    |

|                  | System Clock (HXT) | 3.0V~5.5V       | f <sub>sys</sub> =f <sub>HXT</sub> =8MHz  |       | 8    |       | MHz     |

| f <sub>SYS</sub> |                    | 3.0V~5.5V       | f <sub>sys</sub> =f <sub>Hxt</sub> =16MHz |       | 16   | _     | MHz     |

|                  |                    | 4.5V~5.5V       | f <sub>sys</sub> =f <sub>HXT</sub> =24MHz |       | 24   |       | MHz     |

# **Timing Characteristics**

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified. For HT45B3315: Ta=-40°C~105°C, unless otherwise specified.

| Question            | Demonster                                                                 |               | Test Conditions                                             |      | -    |      | 11               |

|---------------------|---------------------------------------------------------------------------|---------------|-------------------------------------------------------------|------|------|------|------------------|

| Symbol              | Parameter                                                                 | VDD           | Conditions                                                  | Min. | Тур. | wax. | Unit             |

| t <sub>RES</sub>    | External Reset Minimum Low Pulse Width                                    | -             | _                                                           | 10   | —    | _    | μs               |

| +                   | HXT Oscillator Startup Time                                               | 3V            | f <sub>sys</sub> =f <sub>Hxt</sub> =16MHz                   | _    | —    | 25   | ms               |

| tstart(HXT)         | HAT Oscillator Startup Time                                               | 5V            | ISYS-IHXT-TOIVINZ                                           | _    | —    | 10   | ms               |

| t <sub>ckosst</sub> | CLKOUT Start-up Timer Period<br>(Wake up from condition where HXT is off) | _             | f <sub>SYS</sub> =f <sub>HXT</sub>                          | _    | 1024 | _    | t <sub>sys</sub> |

| fizc -              | I <sup>2</sup> C Standard Mode (100kHz) f <sub>SYS</sub> Frequency        | 3.0V~<br>5.5V | No clock debounce                                           | 2    | —    |      | MHz              |

|                     |                                                                           |               | 2 system clock debounce                                     | 4    | —    |      | MHz              |

|                     |                                                                           |               | 4 system clock debounce                                     | 8    | —    |      | MHz              |

| 112C                |                                                                           | 0.01/         | No clock debounce                                           | 5    | —    |      | MHz              |

|                     | I <sup>2</sup> C Fast Mode (400kHz) f <sub>SYS</sub> Frequency            | 3.0V~<br>5.5V | 2 system clock debounce                                     | 10   | —    | _    | MHz              |

|                     |                                                                           | 0.00          | 4 system clock debounce                                     | 20   | _    |      | MHz              |

| f <sub>SPI</sub>    | SPI Mode Frequency                                                        | -             | _                                                           | _    | —    | 10   | MHz              |

| t <sub>ITO</sub>    | I <sup>2</sup> C Timeout Period                                           | 3.0V~<br>5.5V | f <sub>SYS</sub> =f <sub>HXT</sub> =16MHz                   | 40   | _    | _    | ms               |

| t <sub>SOF</sub>    | SOF Signal Width                                                          | _             | f <sub>SYS</sub> =f <sub>HXT</sub> =24MHz,<br>SOFT[2:0]=101 | 9.6  | 10.6 | 11.6 | μs               |

# **CAN Electrical Characteristics**

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified. For HT45B3315: Ta=-40°C~105°C, unless otherwise specified.

| Symbol                   | Parameter               | Test C          | Conditions              | Min.  | Turn | Max. | Unit |

|--------------------------|-------------------------|-----------------|-------------------------|-------|------|------|------|

| Symbol                   | Parameter               | V <sub>DD</sub> | Conditions              | wiin. | Тур. | wax. | Onit |

|                          |                         | —               | f <sub>can</sub> =8MHz  | 3.0   | —    | 5.5  | V    |

| VDD                      | Operating Voltage (HXT) |                 | f <sub>CAN</sub> =16MHz | 3.0   | —    | 5.5  | V    |

|                          |                         |                 | f <sub>CAN</sub> =24MHz | 4.5   | _    | 5.5  | V    |

|                          |                         | 3.0V~5.5V       |                         | _     | 8    |      | MHz  |

| f <sub>CAN</sub>         | System Clock (HXT)      | 3.0V~5.5V       |                         | _     | 16   | _    | MHz  |

|                          |                         | 4.5V~5.5V       |                         | _     | 24   | _    | MHz  |

|                          |                         | 3.0V~5.5V       |                         |       | 8    |      | MHz  |

| <b>f</b> <sub>MCLK</sub> | Memory Clock (HXT)      | 3.0V~5.5V       |                         | _     | 16   | _    | MHz  |

|                          |                         | 4.5V~5.5V       |                         |       | 24   |      | MHz  |

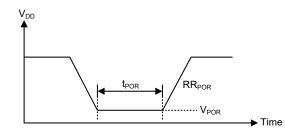

# **Power-on Reset Characteristics**

For HT45B3305H: Ta=-40°C~125°C, unless otherwise specified. For HT45B3315: Ta=-40°C~105°C, unless otherwise specified.

| Symbol | Parameter                                                                           |   | st Conditions | Min.  | Тур. | Max. | Unit |

|--------|-------------------------------------------------------------------------------------|---|---------------|-------|------|------|------|

| Symbol |                                                                                     |   | Conditions    |       |      |      |      |

| VPOR   | V <sub>DD</sub> Start Voltage to Ensure Power-on Reset                              | _ | —             | —     | _    | 100  | mV   |

| RRPOR  | V <sub>DD</sub> Rising Rate to Ensure Power-on Reset                                |   |               | 0.035 | _    | —    | V/ms |

| tpor   | Minimum Time for $V_{\text{DD}}$ Stays at $V_{\text{POR}}$ to Ensure Power-on Reset | _ | _             | 1     |      | _    | ms   |

# **Power Control Function**

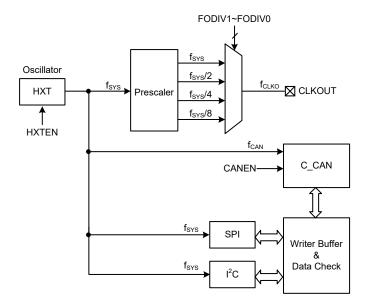

The device operating clock is from an external crystal oscillator, HXT. The oscillator can be enabled or disabled using a register bit HXTEN. The clock which is a divided version of the system clock can be output on the CLKOUT pin.

# **External Crystal Oscillator – HXT**

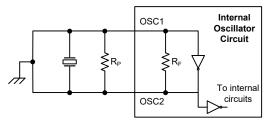

There is a high frequency external crystal oscillator for these devices. For most crystal oscillator configurations, the simple connection of a crystal across OSC1 and OSC2 will create the necessary phase shift and feedback for oscillation, without requiring external capacitors. It is recommended to connect an 8MHz, 16MHz or 24MHz crystal to the HXT pins for applications.

For oscillator stability and to minimise the effects of noise and crosstalk, it is important to ensure that the crystal and any associated resistors and capacitors along with interconnecting lines are all located as close to the devices as possible.

Note: 1. R<sub>P</sub> is normally not required.

2. Although not shown OSC1/OSC2 pins have a parasitic capacitance of around 7pF.

# **CLKOUT Pin**

The clock output pin, CLKOUT is provided to the users for use as a clock input for other devices. The CLKOUT pin has an internal prescaler which can devide  $f_{SYS}$  by 1, 2, 4 and 8. The prescaler is selected via the FOCFG register. When clearing the HXTEN bit in the FOCFG register (ADDRESS: 0xC0) to zero, the HXT oscillator is off thus turning off the CLKOUT clock output.

For the HT45B3315 the CLKOUT pin can be enabled or disabled using the CLKOEN bit in the SFIOSTC register.

# **IDLE Mode**

The IDLE Mode is entered when the HXTEN bit in the FOCFG register is high while the CANEN bit in the CANCFG register is low. In the IDLE Mode the HXT oscillator is continue to provide a clock. The C\_CAN is disabled.

## **SLEEP Mode and Wake-up**

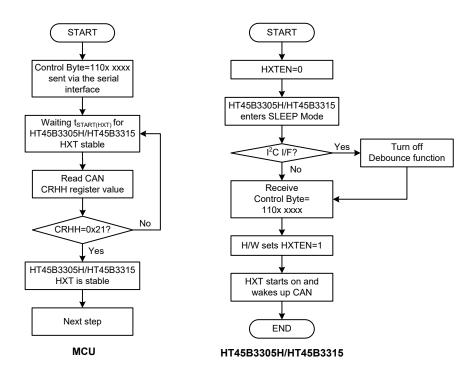

The devices have an internal SLEEP mode that is used to minimize the current consumption of the devices. In the SLEEP Mode the oscillator is turned off. If the I<sup>2</sup>C serial interface is selected, the I<sup>2</sup>C interface debounce function will be disabled after entering the SLEEP Mode. The I<sup>2</sup>C debounce function cannot be used until the first STOP bit on the I<sup>2</sup>C bus is transmitted after the devices are waken up and the HXT output is stable ( $t_{CKOSST}$ ).

To enter the SLEEP mode, the HXTEN bit in the FOCFG register should be cleared to zero. The master can wake up the devices by sending a Wake-up command to set the HXTEN bit high and then read the CRHH register (Address: 0x3B) which indicates whether the HXT oscillator is stable after t<sub>START(HXT)</sub> time. If the CRHH has a value of 21H, it means the HXT oscillator is stable and the devices are success fully waked-up by the master MCU from the SLEEP mode.

# **Functional Description**

The Controller Area Network, or CAN bus for short, is a standard communication protocol used originally designed for automotive networking applications, however it is also used in other application areas such as industrial automation and some entertainment products. It is a two wire serial bus to which the CAN bus equipped products are connected together using twisted pair cable with a characteristic impedence of  $120\Omega$ .

# Write Buffer and Data Check

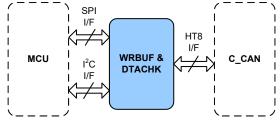

The devices provide a 32-byte Write Buffer with Data check function to easier the communication with Host MCUs and reduce the number of the interface pins between the devices and their Host MCUs.

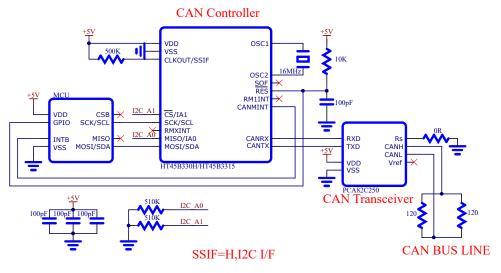

The devices contain two sets of interface modules which are the four line SPI interface and the two line I<sup>2</sup>C interface, to allow an easy method of communication with external Master devices. Having relatively simple communication protocols, these serial interface types allow the devices to interface to external SPI or I<sup>2</sup>C based microcontrollers. The choice of whether the SPI or I<sup>2</sup>C type is used is made using the SSIF pin input signal and with the  $\overline{\text{RES}}$  pin low. Users can choose using SPI or I<sup>2</sup>C serial interface for the data transfer, based on their MCU support interfaces and application speed requirements.

SSIF pin should connect a  $500k\Omega$  pull-low resistor. Communication interface switching is implemented via this pin. During the device reset period which is caused by keeping the  $\overline{\text{RES}}$  pin low, the SSIF pin input can be used to select the serial interface used with the master. The selections are shown in the following table.

When release the  $\overline{\text{RES}}$  pin, the external reset is

| <b>RES &amp; SSIF Conditions</b> | Selected Interface         |

|----------------------------------|----------------------------|

| RES=Low, SSIF=Low                | SPI interface              |

| RES=Low, SSIF=High               | I <sup>2</sup> C interface |

#### Interface Selections

The 32-byte Writter Buffer can be used to store the Control byte, Register Address byte and up to 31 bytes Data which are received or to be transmit in a communication.

## SPI and I<sup>2</sup>C Frame Fields

Following the Communication Protocol, the SPI or I<sup>2</sup>C frame should contain five data fields which are Control Byte, Register Address, Control CheckSum, Data and Data CheckSum.

- A 1-byte control field, including:

- A 3-bit control instruction code defining the operation command.

- A 5-bit data length code bits defining the size (in bytes) of the data field.

- A 1-byte Register Address field, defining the start register address to read from or to write into

- A 1-byte Control CheckSum field, Detecting errors during the control byte and the address byte transmission. The control checksum is based on a XOR operation

- A Data field of up to 31 bytes

- A 1-byte Data CheckSum field, Detecting errors during the data transmission. The control checksum is based on a XOR operation of all write/read data.

## **Control Byte**

For each data transfer, a Control Byte is initiated to specify which Instruction is executed and how many bytes of data is transferred. The bit7~bit5 of the Control Byte, named INSTR[2:0], define the instruction while the bit4~bit0 of the Control Byte, named SDLC[4:0], is the data length code for setting the number of the data bytes to be received or transmitted.

# Serial Data Length Code

The data byte numbers of  $1 \sim 31$  can be determined by programming the SDLC[4:0] bits in the control byte.

| SDLC[4:0]   | Serial Data Length | Description                  |

|-------------|--------------------|------------------------------|

| 00000       | Not Valid          | Not Valid                    |

| 00001~11111 | 1~31               | Valid programmed values 1~31 |

Note: The data length must be defined correctly when the INSTR[2:0] bits are set as 010 or 101. For other instructions, the defining of the data length is not required.

#### Instruction Control Code

The instruction is determined by the INSTR bit field of the control byte.

| INSTR[2:0]        | Instruction | Description                                                                      |

|-------------------|-------------|----------------------------------------------------------------------------------|

| 000 or 001 or 011 | Not Valid   | Not Valid                                                                        |

| 010               | Write Data  | To write data to Buffer                                                          |

| 100               | Read Status | Read HT45B3305H/HT45B3315 status                                                 |

| 101               | Read Data   | To read CAN register data                                                        |

| 110               | Wake Up     | Wake CAN Up                                                                      |

| 111               | Reset       | Reset CAN Block(can_reset) - Resets inter-<br>nal CAN registers to default state |

Note: If set INSTR[2:0]=010 or 101, the SDLC[4:0] bits must be set correctly to define the length of the data to be read or written.

#### Instruction Description

The instruction byte is sent to the devices via the SPI or I<sup>2</sup>C interface for different operations. Refer to "SPI Interface Timing Diagram" or "I<sup>2</sup>C Interface Timing Diagram" for detailed input and output timing diagram.

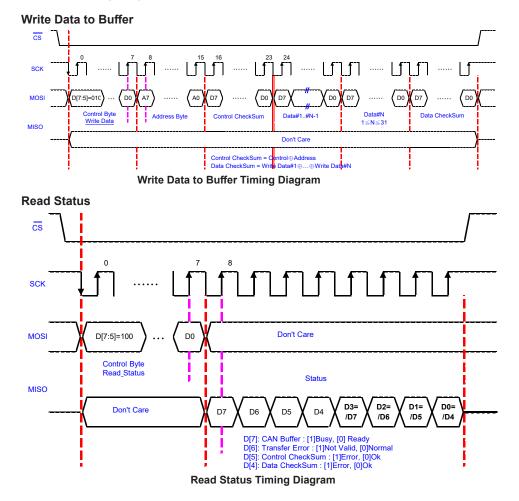

#### Write Data to Buffer

An instruction code of 010B should be transmitted to the devices. The SDLC[4:0] bits in the control byte must be programmed correctly to define the data length to be written. The Register Address field defines the starting register address where the following data will be written into.The register address is automatically incremented by one to store the next byte of data until all the data bytes are written.

A byte Control byte, a byte address byte and the written data bytes will be written into the write buffer. Each transmission of the control and address bytes is followed by a XOR checksum byte for the control and address byte data. And another XOR checksum byte of the data bytes is transferred after the transmission of the data field for detecting errors during the data transmission.

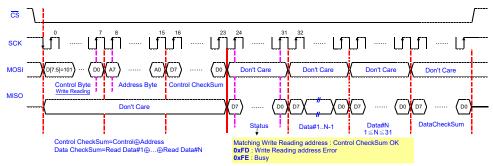

#### **Read CAN Register Data**

An instruction code of 101B should be transmitted to the devices. The SDLC[4:0] bits in the control byte must be programmed correctly to define the data length of reading CAN registers. The Address field byte defines the starting address of the CAN registers that the master wanted to read from. A control checksum byte which computes the exclusive or (XOR) of the control and address data is transmitted for detecting the control and address byte errors. After the control byte, address byte and the checksum byte are sent, the data stored in the registers at the selected starting address can stored in the buffer. The internal register address is automatically incremented by one to read the data and store it to the buffer until the defined SDLC[4+0] bytes of data all were read. And another checksum byte which computes the XOR of the read data is following the data field for detecting data errors. All the data will be shifed out on the MISO pin. Then the master can read the data.

Before reading out the required register data, the first byte read by the master is a simple status byte which is used to determine whether the devices are busy and the reading address is matched or not. Different values of the first byte and the corresponding status they indicate are summaried in the following table:

| 1 <sup>st</sup> Byte= | Description                                                                       |

|-----------------------|-----------------------------------------------------------------------------------|

| Write Address         | It means the register address to read has been written correctly by the host MCU. |

| 0xFD                  | Control CheckSum error.<br>It means a error in writing the reading address        |

| 0xFE                  | HT45B3305H/HT45B3315 Busy                                                         |

| Others                | Don't care                                                                        |

The "Read CAN Register Data" instruction is used to read the device register content and provide brief current error information about the device internal processing status such as access address error and device busy status.

## **Read Status**

The Read Status Instruction allows single instruction access to some bits about the device status.

The part is selected by an instruction code of 100B transmitted to the devices. After the read status instruction is sent by the host, the devices will return eight bits of data that contain the status.

| Status Byte | Description                                                                                                                                                    | Initial Value |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Bit7        | HT45B3305H/HT45B3315 Buffer Busy flag bit<br>0: Ready<br>1: Busy                                                                                               | 0             |

| Bit6        | Transfer Error<br>0: Normal<br>1: INSTR[2:0] value in Control Byte invalid or I <sup>2</sup> C time-out occurred if<br>I <sup>2</sup> C interface was selected | 0             |

| Bit5        | Control CheckSum Error<br>0: Ok<br>1: Error                                                                                                                    | 0             |

| Bit4        | Data CheckSum Error<br>0: Ok<br>1: Error                                                                                                                       | 0             |

| Bit3        | Bit3 = Bit7                                                                                                                                                    | 1             |

| Bit2        | Bit2 = Bit6                                                                                                                                                    | 1             |

| Bit1        | Bit1 = Bit5                                                                                                                                                    | 1             |

| Bit0        | Bit0 = Bit4                                                                                                                                                    | 1             |

In the status byte, Bit3~Bit0 is the Bit3= $\overline{Bit7}$ , Bit2= $\overline{Bit6}$ , Bit1= $\overline{Bit5}$  and Bit0= $\overline{Bit4}$ . This four bit feild is for the purpose of detecting errors about the status bits. So the Checksum field can be omitted.

The Reading Status instruction should be executed in the following conditions:

- Before the initialisation after a reset, it needs first to determine whether the devices are busy or not?

- Reading the device status instruction can be executed after writing data into important registers, to confirm the data was written correctly.

- When using the "Read CAN Register Data" instruction, if the first byte data received by the devices have the value of 0xFD or 0xFE and users need complete error information, then the "Read Status Instruction" can be used to determine the actual condition, such as the device busy, Control CheckSum error, Transfer error or Data CheckSum error.

## Wake CAN Up

If the HXTEN bit is cleared to zero, the HXT oscillator will stop and the devices enter the Sleep Mode. To wake up the devices, an instruction code of 110B can be sent. Refer to the "SLEEP Mode and Wake-up" section for detailed wake-up process.

It needs to note for the wake up instruction, the SDLC[4:0] bits in the Control field and the

following four fields which are Register Address, Control CheckSum, Data and Data CheckSum are not required. But if the frame contains these four fields, the devices will also save them into the buffer without processing them and an error will not happen.

## Reset CAN Block Instruction

The Reset CAN Block Instruction can be used to re-initialise the internal CAN registers of the devices to default state. Only an instruction code of 111B should be transmitted to the devices for the reset operation. The SDLC[4:0] bits in the Control field and the following four fields which are Register Address, Control CheckSum, Data and Data CheckSum are not required. But if the frame contains these four fields, the devices will also store them into the buffer without processing them and an error will not happen.

## **SPI Serial Interface**

The devices are designed to interface directly with the Serial Peripheral Interface (SPI) port available on many microcontrollers. Commands and data are sent to the devices via the MOSI pin, with data being clocked in on the rising edge of SCK. Data is driven out by the devices, on the MISO line, on the falling edge of SCK. The  $\overline{CS}$  pin must be held low while any operation is performed. When raising the  $\overline{CS}$  pin from low to high, the SPI Interface will be reset.

Note: Wait 10 HXT clocks for every 8 bits of command/position/data.

## SPI Interface Timing Diagrams

Rev. 1.40

## **Read CAN Register Data**

Read CAN Register Data Timing Diagram

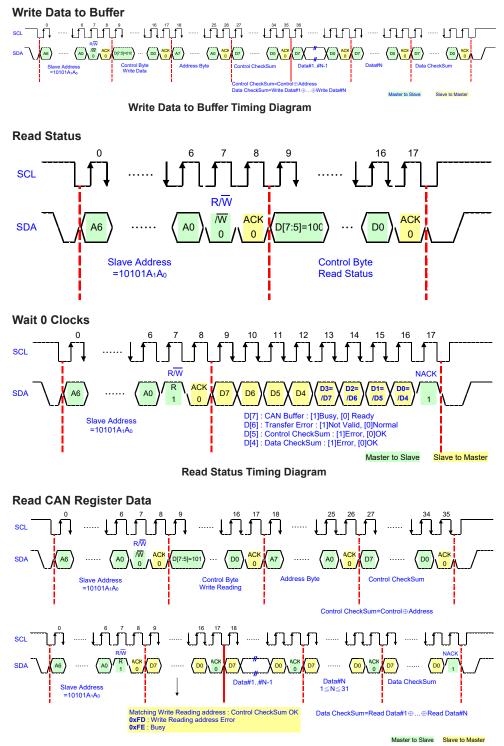

# I<sup>2</sup>C Serial Interface

During the device reset with the  $\overline{\text{RES}}$  pin held low, setting the SSIF pin input high, then the I<sup>2</sup>C interface function together with SCL and SDA pin functions are selected; the I<sup>2</sup>C interface is used for communication with the master.

The I2CDEB1 and I2CDEB0 bits in the FOCFG register determine the debounce time of the  $I^2C$  interface. This uses the internal clock to in effect add a debounce time to the external clock to reduce the possibility of glitches on the clock line causing erroneous operation. The debounce time, if selected, can be chosen to be either 2 or 4 system clocks. There is also an option of no debounce can be selected.

## I<sup>2</sup>C Slave Address

The slave address byte is the first byte received following the START condition from the master device. The first seven bits of the first byte make up the slave address. The eighth bit defines a read or write operation to be performed. When this  $R/\overline{W}$  bit is "0", then a write operation is selected. A "1" selects a read operation. The device address bits are "10101A<sub>1</sub>A<sub>0</sub>" where the "A<sub>1</sub>, A<sub>0</sub>" value should be the IA1, IA0 pin external level. When an address byte is sent, the devices compare the first seven bits after the START condition. If they match, the devices output an acknowledge on the SDA line.

| IA1 Pin<br>Level | IA0 Pin<br>Level | I <sup>2</sup> C Slave Address<br>(10101A <sub>1</sub> A <sub>0</sub> ) |

|------------------|------------------|-------------------------------------------------------------------------|

| Low              | Low              | 1010100                                                                 |

| Low              | High             | 1010101                                                                 |

| High             | Low              | 1010110                                                                 |

| High             | High             | 1010111                                                                 |

I<sup>2</sup>C Slave Address definition:

## I<sup>2</sup>C Timeout Function

In order to reduce the I<sup>2</sup>C data transfer problem due to reception of erroneous clock sources, a time-out function is provided. When the devices are receiving data via the I<sup>2</sup>C interface, a SCL low level keeps for a time over the specified timeout period of  $t_{\rm ITO}$ , the I<sup>2</sup>C interface will be reset. In the SLEEP mode (HXTEN=0), if the I<sup>2</sup>C interface is being used, the timeout function is still effective.

## I<sup>2</sup>C Interface Timing Diagrams

Read CAN Register Data Timing Diagram

# HT45B3305H/HT45B3315 CAN Block Diagram

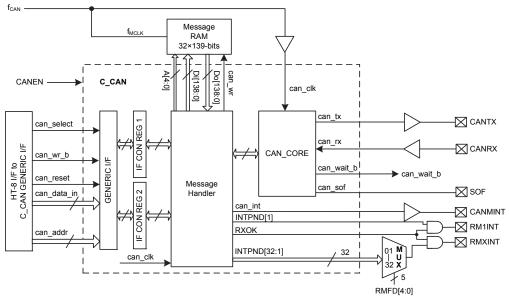

The Holtek CAN Module licensed from Bosch which supports CAN communication with up to 8 byte data fields. The devices implement the HT45B3305H/HT45B3315 CAN. As the same with the C\_CAN, the HT45B3305H/HT45B3315 CAN consists of the components CAN Core, Message RAM, Message Handler, Interface Control Register sets. A HT-8 Interface to C\_CAN generic interface is provided by the HT45B3305H/HT45B3315 CAN, via which the external 8-bit MCUs could access the C\_CAN registers.

HT45B3305H/HT45B3315 CAN Block Diagram

# 1. C\_CAN Core

Refer to the following Operating Description and Application section for further CAN module operation details. In this section we give a description about the functional blocks of the C\_CAN:

• CAN\_Core

The CAN\_Core performs communication according to the CAN protocol version 2.0 A, B and ISO 11898-1.

Registers

All registers are used to control and to configure the module.

• Message Handler

The internal State Machine controls the data transfer between the RX/TX Shift Register of the CAN\_Core and the Message RAM as well as the generation of interrupts as programmed in the Control and Configuration Registers. All functions concerning the handling of messages are implemented in the Message Handler. Those functions are the acceptance filtering, the transfer of messages between the CAN Core and the Message RAM, and the handling of transmission requests as well as the generation of the module interrupt.

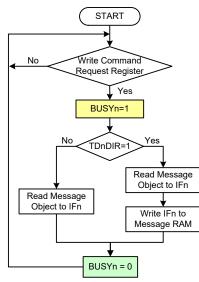

• Interface Control Register 1 and 2

The function of the two interface control register sets is identical (except in Basic mode). The interface control register sets are used for the data transfer between the external bus and the Message RAM.

Message RAM Interface Message RAM size: 139-bits×32

#### 2. Message RAM IP

- Stores 32 Message Objects and Identifier Masks.

- Each Message Object together with Identifier Mask has a length of 139 bits.

#### 3. HT-8 interface to C\_CAN Generic Interface

- The external 8-bit microcontroller can access the C\_CAN registers through this transform interface.

- By the firmware, the MCU defined the desired register address. It is only allowed to access one register each time. To implement consecutive access operations, the address should be incremented by one using the firmware.

## **Interrupt Output Pins**

The devices have three interrupt output pins, CANMINT, RM1INT and RMXINT, to be used to indicate different conditions. When a CAN interrupt occurs, the CANMINT pin will be driven an active level by the devices. When a Message is received into Message Object 1 successfully, an interrupt occurs and the RM1INT pin will output an active level. When a Message is received into Message Object x successfully, an interrupt occurs and the RMXINT pin will output an active level.

Interrupt active level can be selected to be high or low using the FOCFG register bits.

## Message RAM and FIFO Buffer Configuration

For communication on a CAN network, individual Message Objects are configured. The Message Objects and Identifier Masks for acceptance filtering of received messages are stored in the Message RAM. The devices include a Message Memory capacity of 139-bit ×32 for storing 32 Message Objects and Identifier Masks. A Message Objects and Identifier Masks is 139 bits which is shown in the following table.

| Structure of a Message Object in the Message RAM |       |       |         |        |        |        |           |

|--------------------------------------------------|-------|-------|---------|--------|--------|--------|-----------|

| MSKn28~00                                        | MXTDn | MDIRn | UMASKn  | TXnIEN | RXnIEN | RMTnEN | EOBn      |

| IDn28~00                                         | XTDn  | DIRn  | MSGnLST | —      | —      | _      | DLCn[3:0] |

| DATA0                                            | DATA1 | DATA2 | DATA3   | DATA4  | DATA5  | DATA6  | DATA7     |

#### MSKn28~00 Identifier Mask

0: The corresponding bit in the identifier of the message object cannot inhibit the match in the acceptance filtering

1: The corresponding identifier bit is used for acceptance filtering

| IDn28~00 | Message Identifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | IDn28~IDn00: 29-bit Identifier ("Extended Frame").                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          | IDn28~IDn18: 11-bit Identifier ("Standard Frame").                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MXTDn    | <ul> <li>Mask Extended Identifier</li> <li>0: The extended identifier bit (IDE) has no effect on the acceptance filtering</li> <li>1: The extended identifier bit (IDE) is used for acceptance filtering</li> <li>Note: When 11-bit ("standard") Identifiers are used for a Message Object, the identifiers of received Data Frames are written into bits IDn28 to IDn18. For acceptance filtering, only these bits together with MASK bits MSKn28 to MSKn18 are considered.</li> </ul> |

| XTDn     | Extended Identifier<br>0: The 11-bit ("standard") Identifier will be used for this Message Object<br>1: The 29-bit ("extended") Identifier will be used for this Message Object                                                                                                                                                                                                                                                                                                         |

**MDIRn** Mask Message Direction 0: The message direction bit (DIR) has no effect on the acceptance filtering 1: The message direction bit (DIR) is used for acceptance filtering Note: The Arbitration Registers IDn28-00, XTDn, and DIRn are used to define the identifier and type of outgoing messages and are used (together with the mask registers MSKn28-00, MXTDn, and MDIRn) for acceptance filtering of incoming messages. A received message is stored into the valid Message Object with matching identifier and Direction=receive (Data Frame) or Direction=transmit (Remote Frame). Extended frames can be stored only in Message Objects with XTDn=one, standard frames in Message Objects with **XTDn**=zero. If a received message (Data Frame or Remote Frame) matches with more than one valid Message Object, it is stored into that with the lowest message number. For details see chapter Acceptance Filtering of Received Messages. DIRn Message Direction 0: Direction=receive: On TREQ, a Remote Frame with the identifier of this Message Object is transmitted. On reception of a Data Frame with matching identifier, that message is stored in this Message Object. 1: Direction=transmit: On TREQ, the respective Message Object is transmitted as a Data Frame. On reception of a Remote Frame with matching identifier, the **TREQ** bit of this Message Object is set (if RMTnEN=one). UMASKn Use Acceptance Mask 0: MASK ignored. 1: Use MASK (MSKn28~00, MXTDn and MDIRn) for acceptance filtering. If the UMASKn bit is set to one, the Message Object's mask bits have to be programmed during initialization of the Message Object before MSGnVA is set to one. MSGnLST Message Lost (only valid for Message Objects with direction=receive) 0: No message lost since last time this bit was reset by the CPU. 1: The Message Handler stored a new message into this object when NDTA was still set, the CPU has lost a message. **TXnIEN** Transmit Interrupt Enable 0: INTPND will be left unchanged after the successful transmission of a frame. 1: INTPND will be set after a successful transmission of a frame. **RXnIEN** Receive Interrupt Enable 0: INTPND will be left unchanged after a successful reception of a frame. 1: INTPND will be set after a successful reception of a frame. RMTnEN Remote Enable 0: At the reception of a Remote Frame, TREQ is left unchanged. 1: At the reception of a Remote Frame, TREQ is set. EOBn End of Buffer 0: Message Object belongs to a FIFO Buffer and is not the last Message Object of that FIFO Buffer. 1: Single Message Object or last Message Object of a FIFO Buffer. This bit is used to concatenate two ore more Message Objects (up to 32) to build a FIFO Buffer. For single Message Objects (not belonging to a FIFO Buffer) this bit must always be set to one. DLCn3~0 Data Length Code 0~8: CAN: Frame has 0-8 data bytes 9~15: CAN: Frame has 8 data bytes Note: The Data Length Code of a Message Object must be defined the same as in all the corresponding objects with the same identifier at other nodes. When the Message Handler stores a data frame, it will write the DLC to the value given by the received message.

- DATA0 1st data byte of a CAN Data Frame

- DATA1 2nd data byte of a CAN Data FrameDATA2 3rd data byte of a CAN Data Frame

- **DATA2** 3rd data byte of a CAN Data Frame

- DATA3 4th data byte of a CAN Data FrameDATA4 5th data byte of a CAN Data Frame

- DATA4 5th data byte of a CAN Data FrameDATA5 6th data byte of a CAN Data Frame

- **DATA5** 6th data byte of a CAN Data Frame

- **DATA6** 7th data byte of a CAN Data Frame

- DATA7 8th data byte of a CAN Data Frame

- Note: Byte **DATA0** is the first data byte shifted into the shift register of the CAN Core during a reception, byte **DATA7** is the last. When the Message Handler stores a Data Frame, it will write all the eight data bytes into a Message Object. If the Data Length Code is less than 8, the remaining bytes of the Message Object will be overwritten by **non specified values**.

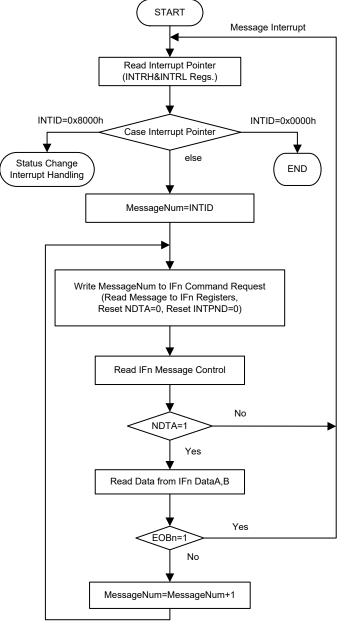

The 32 Message Objects can be configurated to several sets of FIFO buffer. A FIFO buffer can have a single Message Object or several concatenated Message Objects. The FIFO threshold of the Message Object number is determined by the RMFD[4:0] bits in the HT45B3305H/HT45B3315 CAN Configuration Register, CANCFG. When the Message Object of the selected number is received successfully, an interrupt active signal will output on the RMXINT pin.

# HT45B3305H/HT45B3315 CAN Operating Modes

The Operating modes can be controlled by the registers. Detailed informations about the operating modes refer to the following contents and the related registers.

# Software Initialization

The software initialization is started by setting the bit **INIT** in the CAN Control Register, either by software or by a hardware reset, or by going Bus\_Off.

While **INIT** is set, all message transfered from and to the CAN bus is stopped, the status of the CAN bus output **can\_tx** is recessive (HIGH). The counters of the EML(Error Management Logic) are unchanged. Setting **INIT** does not change any configuration register.

To initialize the CAN Controller, the CPU has to set up the Bit Timing Register and each Message Object. If a Message Object is not needed, it is sufficient to set it's **MSGnVA** bit to not valid. Otherwise, the whole Message Object has to be initialized.

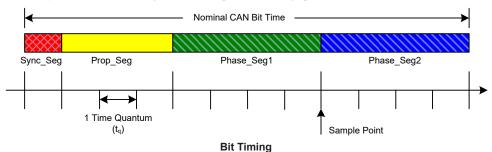

Access to the Bit Timing Register and to the BRP Extension Register for the configuration of the bit timing is enabled when both bits **INIT** and **CCE** in the CAN Control Register are set.